1 概述

OSERDES2--Output Parallel-to-Serial Logic Resources,即输出的串并转换资源,官方手册给出的说明如下:

xilinx 7 系列器件中的 OSERDESE2 是一种专用的并行到串行转换器,具备特定的时钟和逻辑资源,旨在便于实现高速源同步接口。

每个 OSERDESE2 模块都包含一个用于数据和三态控制的专用串行器。数据串行器和三态串行器都可以配置为单数据率(SDR) 和双数据率(DDR) 模式。数据串行化比率最高可达 8:1(如果使用 OSERDESE2 宽度扩展功能,则可达10:1和14:1)。三态串行化比率最高可达 14:1。还有一种专用的 DDR3 模式,用于支持高速内存应用。

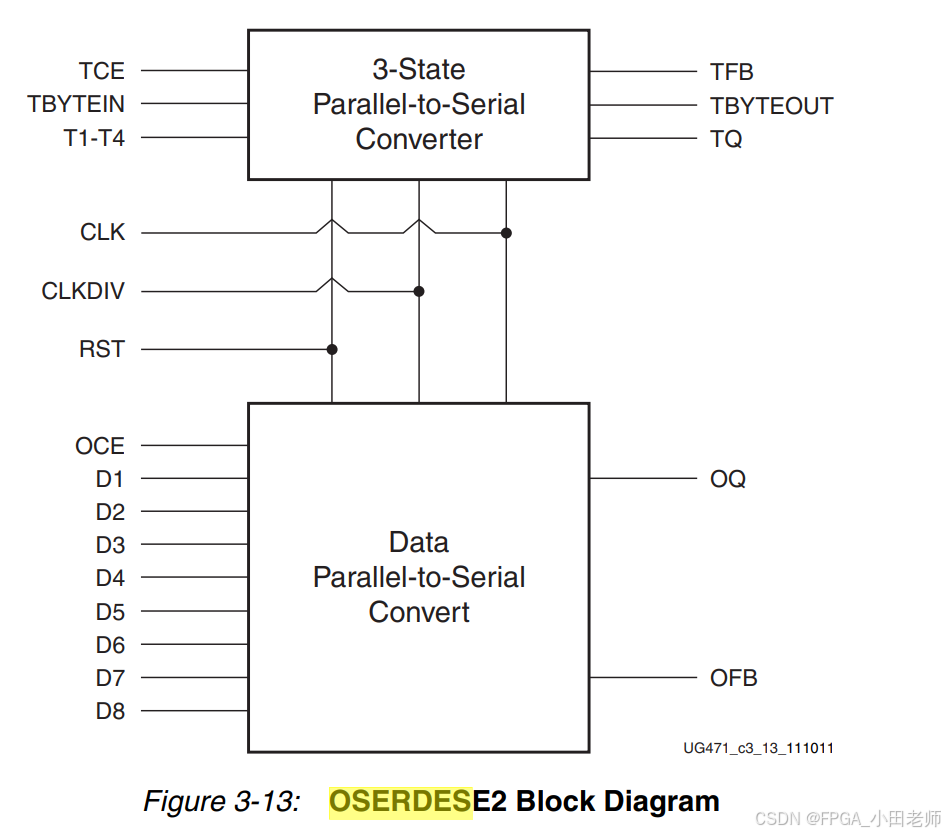

OSERDES2的框图如下,突出显示了该模块的所有组件和特性。

2 OSERDES原语详细说明

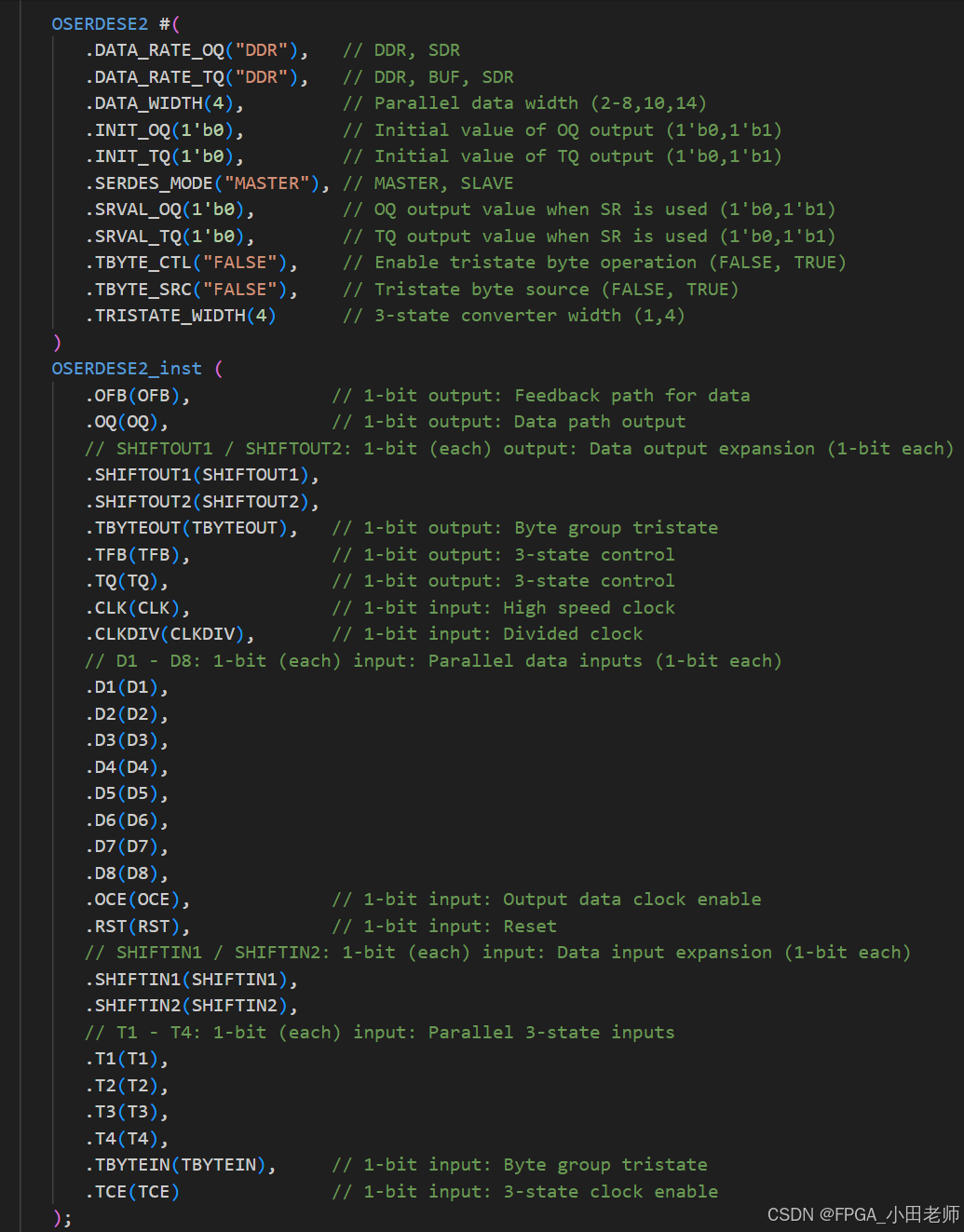

在vivado中获取OSERDES2原语模板,获取方式参考FPGA基础知识(二十一):xilinx FPGA中常用的原语_fpga常用原语-CSDN博客

获取原语模板如下

2.1 Parameter属性说明

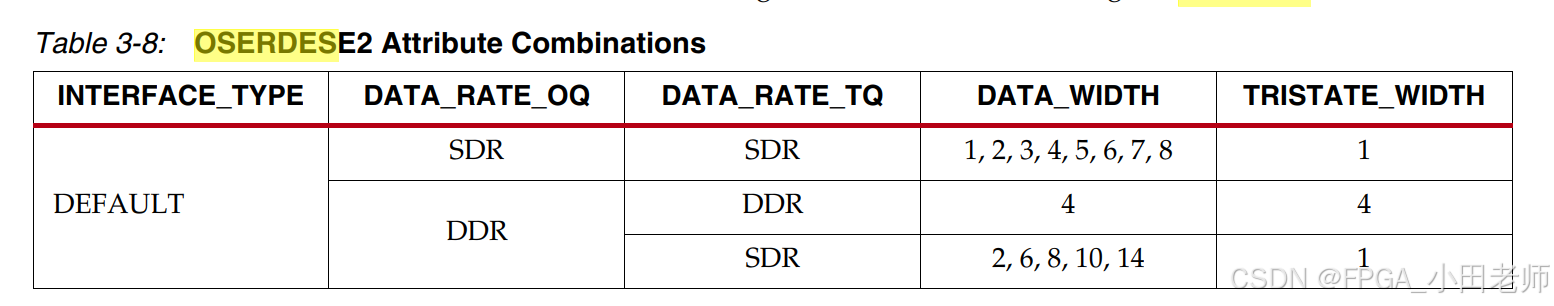

DATA_RATE_OQ:定义了数据是作为单数据速率(SDR:只在时钟上升沿变化)还是双数据速率(DDR:时钟上升沿和下降沿都变化)进行处理。该属性允许的值为 SDR 和 DDR。默认值为 DDR。

**DATA_RATE_TQ:**定义了三态控制是要作为单数据速率(SDR)还是双数据速率(DDR)来处理。此属性允许的值为SDR(上升沿变化)、DDR(双边沿变化)或BUF(只作为缓冲)。默认值为DDR。在SDR和DDR模式下,会使用四个T输入,并且可以使用TRISTATE_WIDTH属性来配置它们的行为。在BUF模式下,会绕过SDR和DDR模式寄存器,因此,应使用T1输入。施加到T1输入的信号与所有其他信号异步,因为它只是直接通过OSERDESE2。

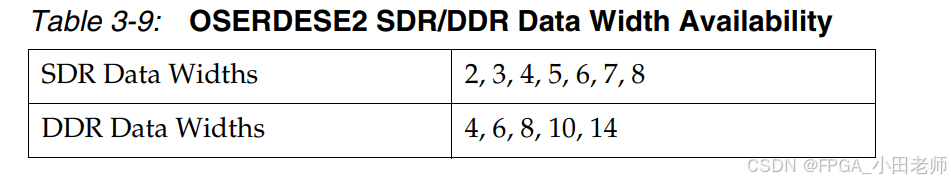

**DATA_WIDTH:**定义了并串转换器的并行数据输入宽度。该属性的可能取值取决于DATA_RATE_OQ属性。当DATA_RATE_OQ设置为SDR时,DATA_WIDTH属性的可能取值为2、3、4、5、6、7和8。当DATA_RATE_OQ设置为DDR时,DATA_WIDTH属性的可能取值为4、6、8、10和14。 当DATA_WIDTH设置为大于8的宽度时,必须将一对OSERDESE2配置为主从配置。请参阅 章节3:OSERDESE2宽度扩展。

**SERDES_MODE:**定义了在使用宽度扩展时,OSERDESE2 模块是主模块还是从模块。可能的值为 MASTER(主)和 SLAVE(从)。默认值为 MASTER(主)。请参阅 章节3:OSERDESE2 宽度扩展。

**TRISTATE_WIDTH:**定义了三态控制并串转换器的并行三态输入宽度。该属性的可能取值取决于 DATA_RATE_TQ 属性。当 DATA_RATE_TQ 设置为 SDR 或 BUF 时,TRISTATE_WIDTH 属性只能设置为 1。当 DATA_RATE_TQ 设置为 DDR 时,TRISTATE_WIDTH 属性的可能取值为 1 和 4。 TRISTATE_WIDTH 不能设置为大于 4 的宽度。当 DATA_WIDTH 大于 4 时,将 TRISTATE_WIDTH 设置为 1。

2.2 输入输出端口说明

2.2.1 时钟与复位

**CLK:**High-Speed Clock Input ----- 这个高速时钟输入 驱动 并行-串行转换器的串行端。

**CLKDIV:**Divided Clock Input-------这个分频后的高速时钟输入 驱动 并串转换器的并行端。

**RST:**当置位时,复位输入会使 CLK 和 CLKDIV 域中所有数据触发器的输出异步拉低。当与 CLKDIV 同步撤销置位时,内部逻辑会将该撤销置位操作重新同步到 CLK 的第一个上升沿。因此,多位输出结构中的每个 OSERDESE2 都应由同一个复位信号驱动,该信号异步置位,并与 CLKDIV 同步撤销置位,以确保所有 OSERDESE2 元件同步退出复位状态。只有在已知 CLK 和 CLKDIV 稳定且存在时,才应撤销复位信号的置位。

2.2.2 数据专用串行器转换端口说明

输出:

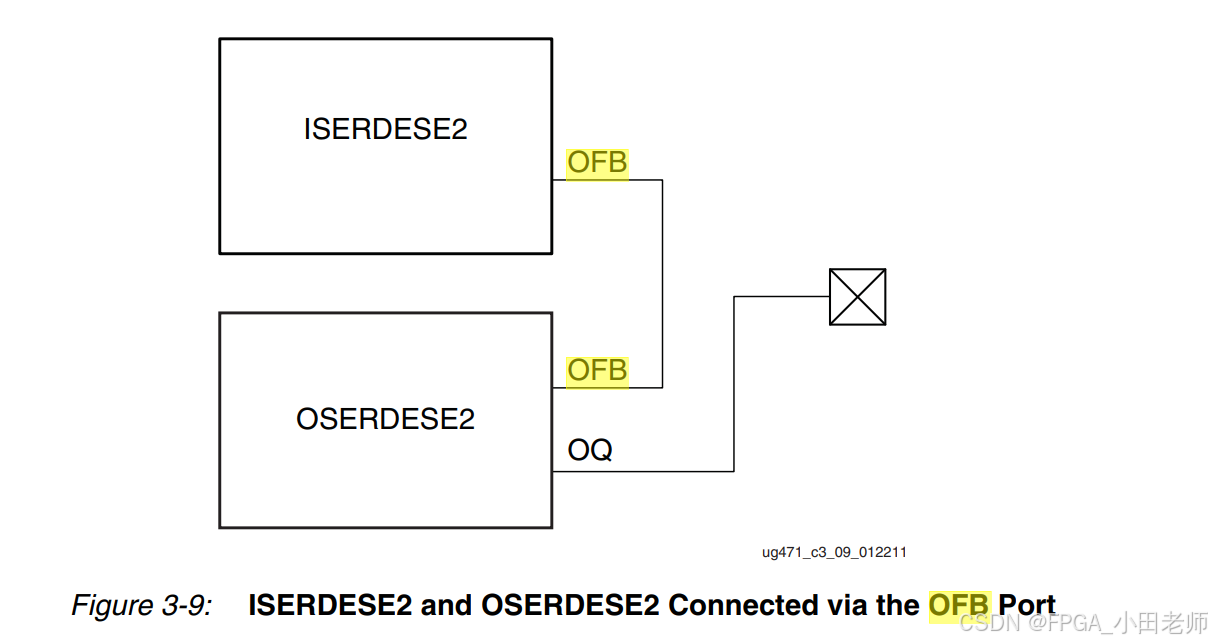

**OFB:**Output Feedback from OSERDESE2------输出反馈端口 (OFB) 是 OSERDESE2 的串行(高速)数据输出端口,用于与 ODELAYE2 原语配合使用,或者 OFB 端口可用于将串行数据发送到 ISERDESE2。

OQ:Data Path Output----OQ端口是OSERDESE2模块的数据输出端口。输入端口D1的数据将首先出现在OQ端口。该端口将数据并串转换器的输出连接到IOB的数据输入。此端口无法驱动ODELAYE2(因为其必须连接到外部输出引脚上);必须使用OFB引脚。

输入:

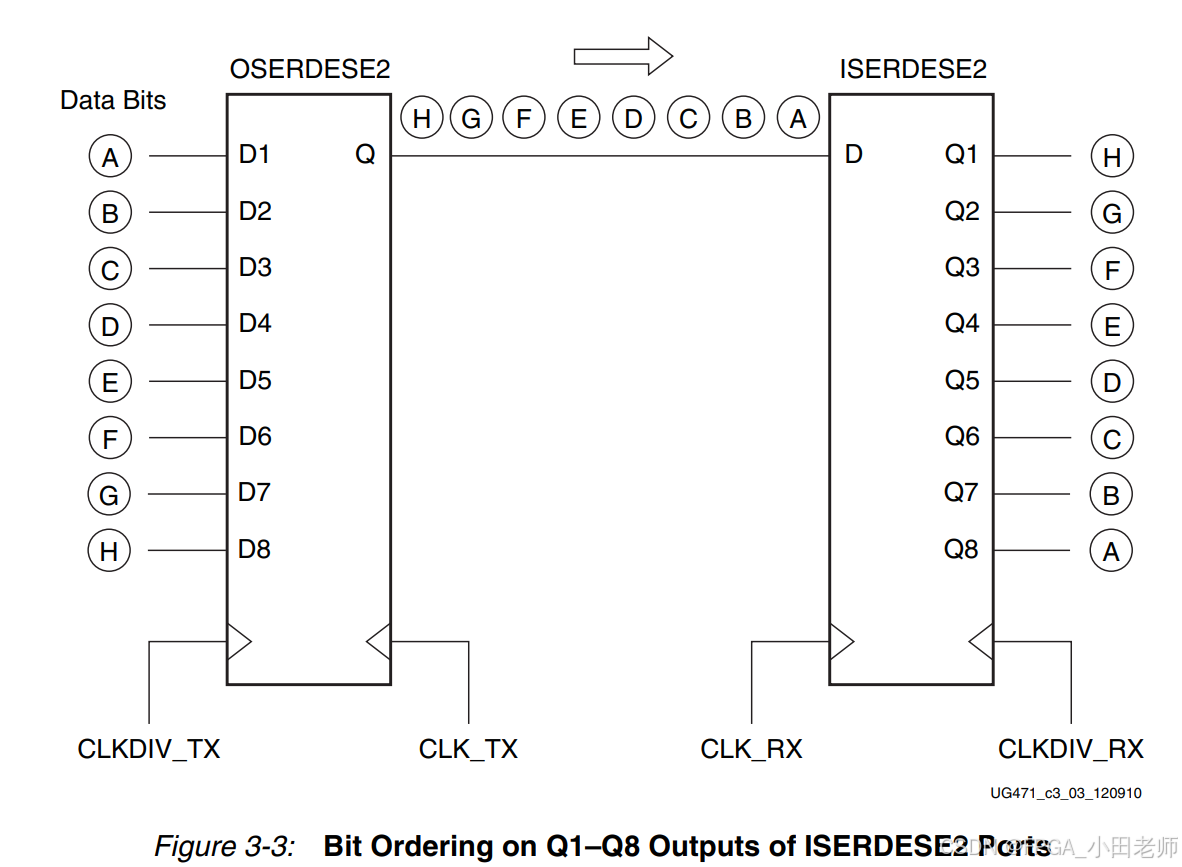

**D1 to D8:**Parallel Data Inputs------所有输入的并行数据通过端口 D1 至 D8 进入 OSERDESE2 模块。这些端口连接到 FPGA 架构,并且可以配置为 2 至 8 位(即 8:1 串行化)。通过使用处于从模式的第二个 OSERDESE2 可以支持大于 8 位(10 位和 14 位)的位宽。请参阅 章节3:OSERDESE2 位宽扩展。有关 OSERDESE2 输入和输出处的位顺序以及 ISERDESE2 的相应位顺序,请参考下图。

**OCE:**Output Data Clock Enable-----数据路径的时钟有效信号,高有效

2.2.3 三态控制专用串行器转换端口说明

输出:

**TFB:**3-state Control Output-----此端口是 OSERDESE2 模块发送到架构的三态控制输出。它表示 OSERDESE2 处于三态。

**TBYTEOUT:**字节组三态输出

**TQ:**该端口是 OSERDESE2 模块的三态控制输出。使用时,该端口将三态并串转换器的输出连接到 IOB 的控制/三态输入

输入:

**TCE:**三态控制路径的时钟使能,高有效

**TBYTEIN:**字节组三态输入

**T1 to T4:**所有并行三态信号通过端口 T1 至 T4 进入 OSERDESE2 模块。这些端口连接到 FPGA 结构。它们可以配置为 1 位、2 位或 4 位,也可以旁路。这些端口的行为由 DATA_RATE_TQ 和 TRISTATE_WIDTH 属性控制。

2.2.4 扩展信号相关

SHIFTIN1、SHIFTIN2、SHIFTOUT1、SHIFTOUT2,后续章节详细介绍。

3 OSERDES2的宽度扩展

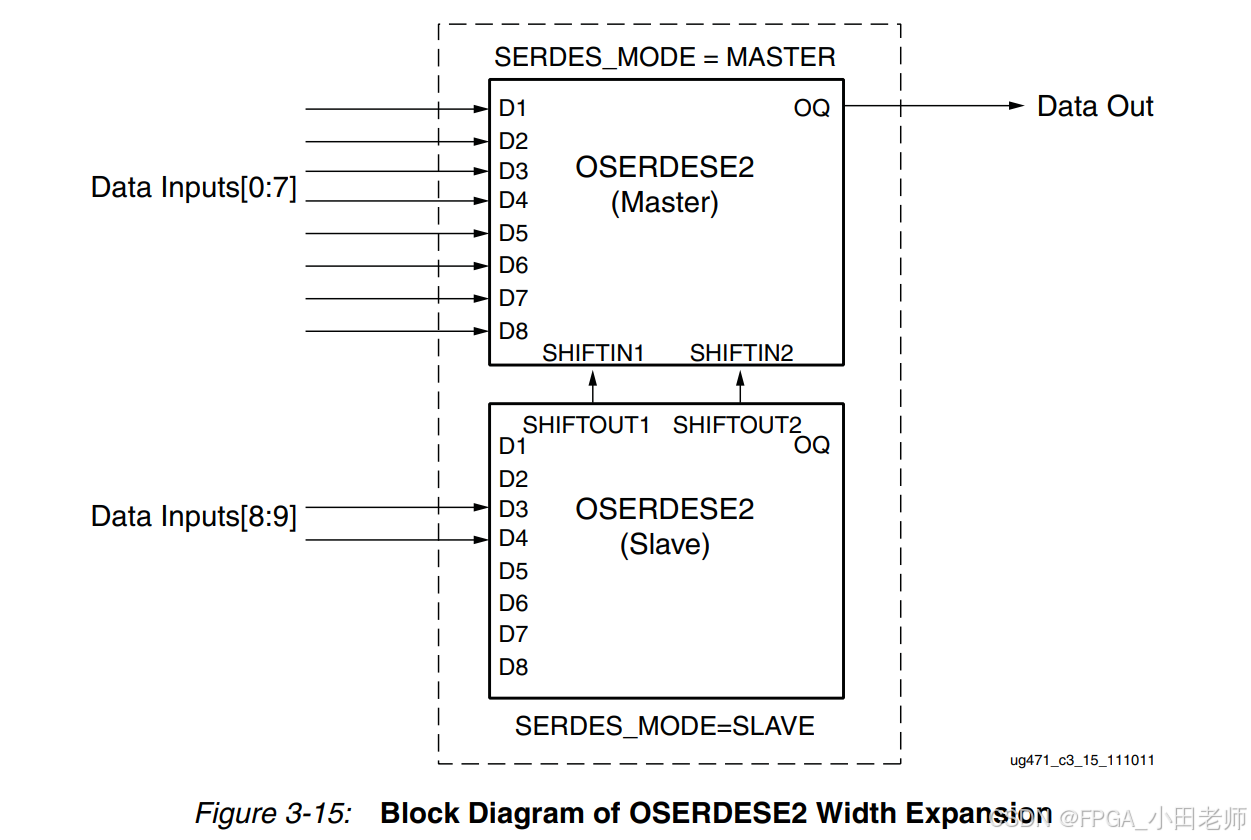

OSERDESE2模块可用于构建大于8:1的并串转换器。在每个I/O模块中,有两个OSERDESE2模块:一个主模块和一个从模块。通过将主OSERDESE2的SHIFTIN端口连接到从OSERDESE2的SHIFTOUT端口,该并串转换器可扩展至最高10:1和14:1(仅在DDR模式下)。对于差分输出,主OSERDESE2必须位于差分输出对的正(_P引脚)侧。当输出不是差分输出时,与从OSERDESE2关联的输出缓冲器不可用,且无法使用宽度扩展功能。

当使用互补单端标准(例如,DIFF_HSTL和DIFF_SSTL)时,可能无法使用宽度扩展功能。这是因为I/O模块中的两个OLOGICE2/3模块被互补单端标准用于传输两个互补信号,从而没有可用的OLOGICE2/3模块用于宽度扩展。

下图展示了一个使用主从OSERDESE2模块的10:1 DDR并串转换器的框图。在这种情况下,端口D3 - D4用于从OSERDESE2上并行接口的最后两位。

并行转串行转换器位宽扩展必须遵循以下要求:

- 两个 OSERDESE2 模块必须是相邻的主从对。

- 将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,从 OSERDESE2 的该属性设置为 SLAVE。请参阅 SERDES_MODE 属性说明。

- 用户必须将主模块的 SHIFTIN 端口连接到从模块的 SHIFTOUT 端口。

- 从模块仅使用 D3 至 D8 端口作为输入。

- 主模块和从模块的 DATA_WIDTH 相等。请参阅 DATA_WIDTH 属性说明。

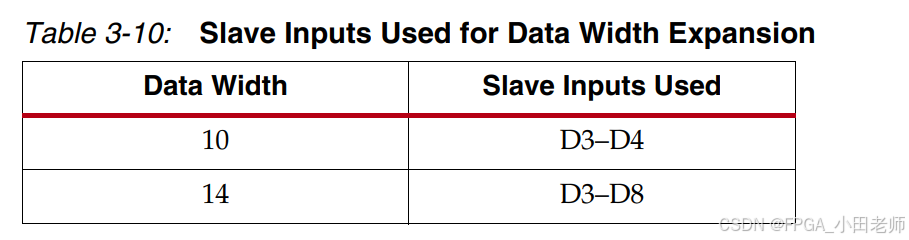

- INTERFACE_TYPE 属性设置为 DEFAULT。 需要进行位宽扩展的数据位宽所使用的从模块输入列于表 。

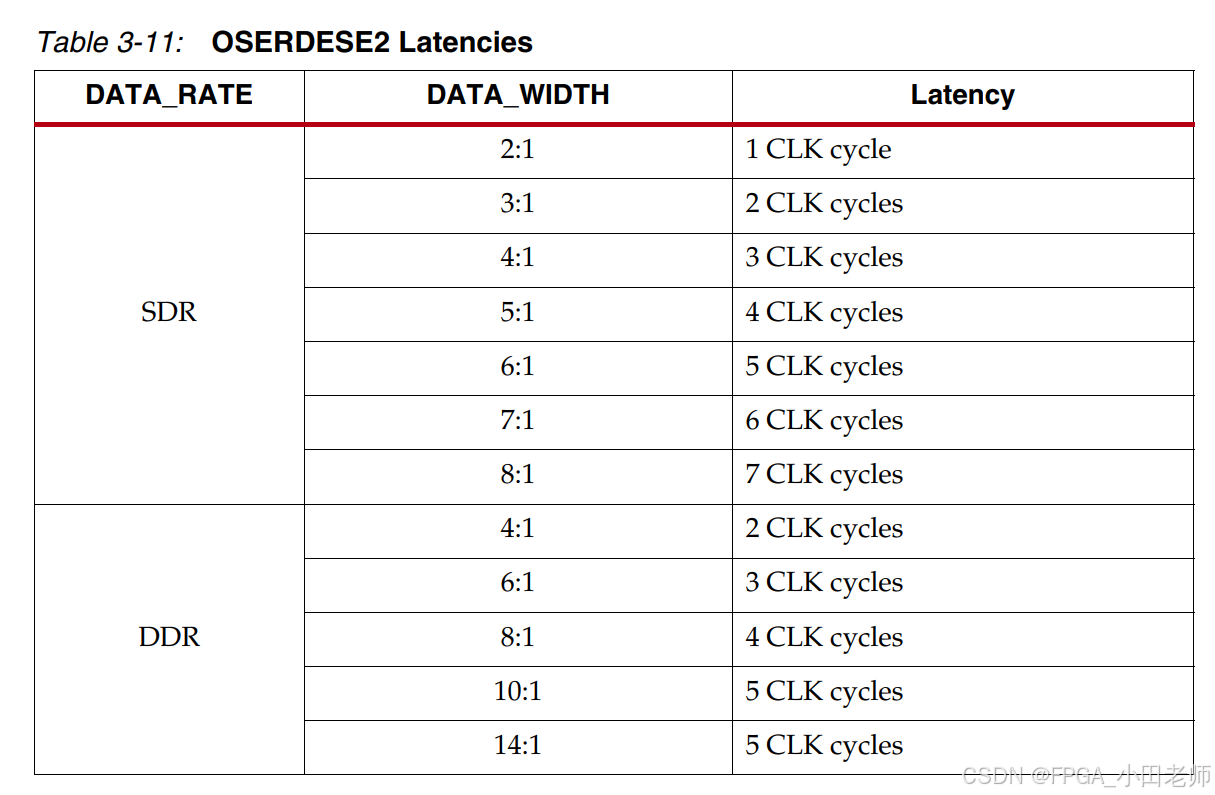

4 OSERDES2的延迟

OSERDESE2 模块的输入到输出延迟取决于 DATA_RATE 和 DATA_WIDTH 属性。延迟定义为以下两个事件之间的一段时间0:

(a) 当 CLKDIV 的上升沿将输入 D1 - D8 处的数据锁存到 OSERDESE2 中时;

(b) 当串行数据流的第一位出现在 OQ 处时。

下表总结了各种 OSERDESE2 延迟值,通常CLK 和 CLKDIV 时钟边沿通常并非相位对齐。当两个时钟的边沿相位对齐时,延迟可能会相差一个周期。

5 OSERDES2的时序

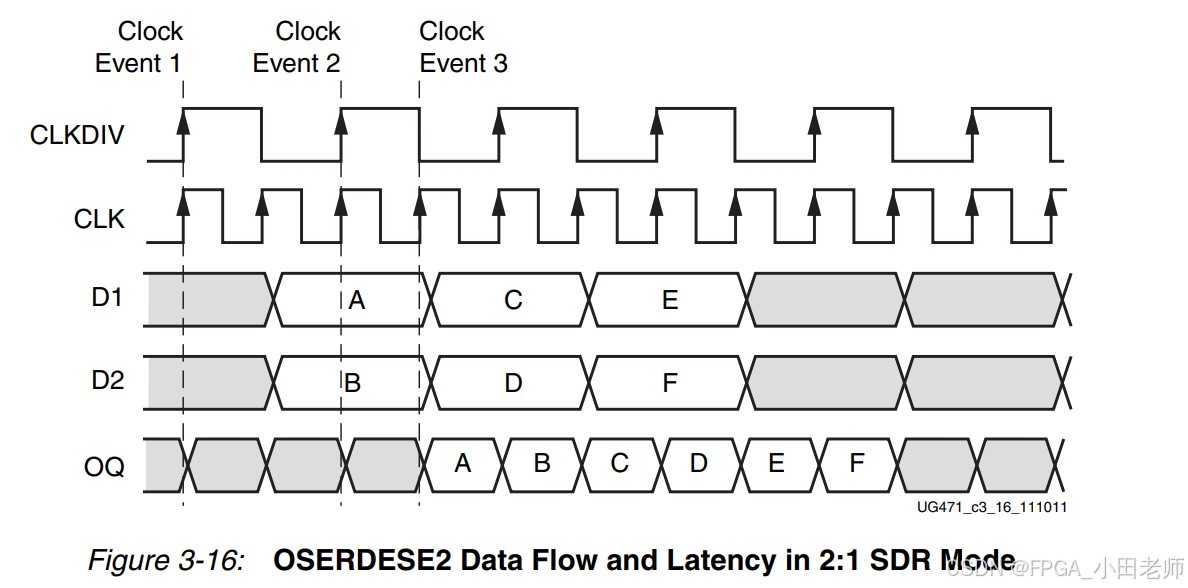

5.1 2:1 单数据率(SDR)串行化的时序

Clock Event 1 :在 CLKDIV 的上升沿,字 AB 从 FPGA 逻辑驱动到 OSERDESE2 的 D1 和 D2 输入(经过一些传播延迟后)。

Clock Event2: 在 CLKDIV 的上升沿,字 AB 从 D1 和 D2 输入采样到 OSERDESE2 中。

Clock Event3: 在 AB 被采样到 OSERDESE2 中一个 CLK 周期后,数据位 A 出现在 OQ 端。

这种延迟与上表中列出的 2:1 SDR 模式 OSERDESE2 一个 CLK 周期的延迟一致。

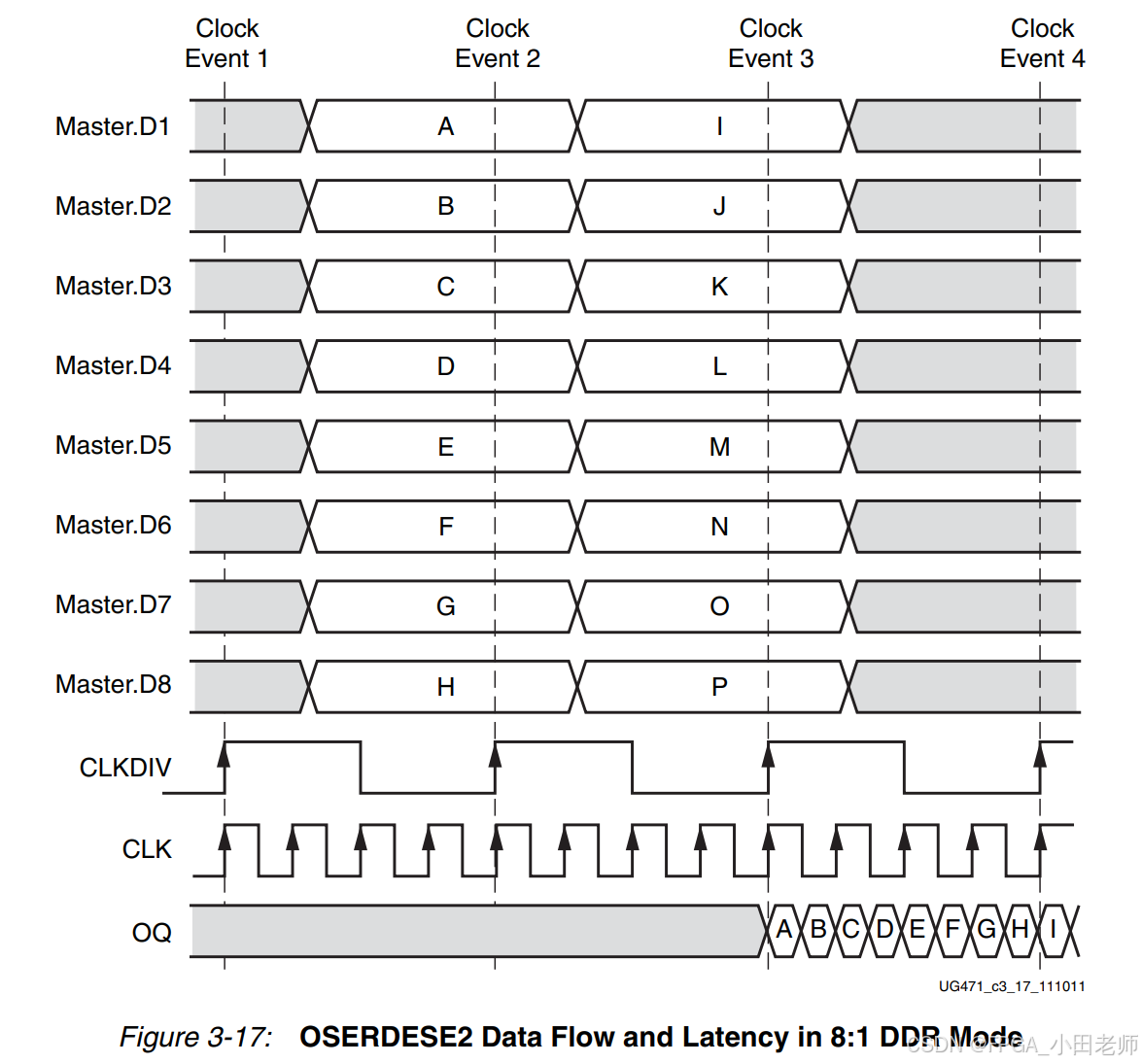

5.2 8:1 DDR 串行化的时序

下图展示了 8:1 DDR 数据串行化的时序。所有 8 位数据都连接到主 OSERDESE2 的 D1 - D8。

Clock Event1: 在 CLKDIV 的上升沿,字 ABCDEFGH 从 FPGA 逻辑驱动到 OSERDESE2 的 D1 - D8 输入。

Clock Event1: 在 CLKDIV 的上升沿,字 ABCDEFGH 从 FPGA 逻辑驱动到 OSERDESE2 的 D1 - D8 输入。

Clock Event2:在 CLKDIV 的上升沿,字 ABCDEFGH 从 D1 - D8 采样到 OSERDESE2 中。

Clock Event3:时钟事件 3 在 ABCDEFGH 采样到 OSERDESE2 中之后的四个 CLK 周期,数据位 A 出现在 OQ 端。

这种延迟与上表中列出的 8:1 DDR 模式 OSERDESE2 四个 CLK 周期的延迟一致。

Clock Event4: 在Clock Event3和Clock Event4之间,整个单词ABCDEFGH在OQ上串行传输,在一个CLKDIV周期内总共传输8位。

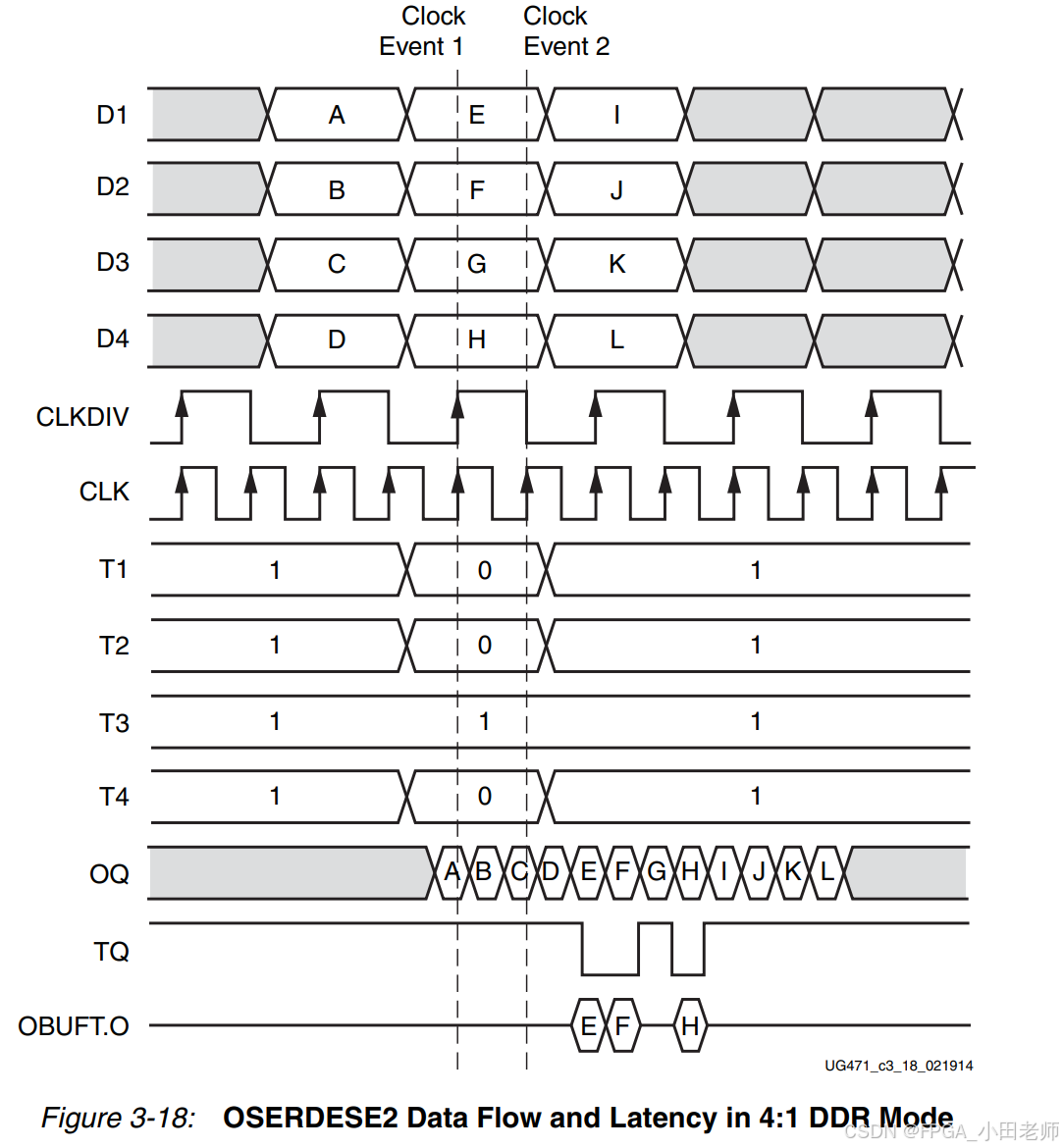

5.3 4:1 双倍数据速率(DDR)三态控制器的时序

下图展示了三态控制器的工作原理。此示例为 4:1 DDR 情况,应用于双向系统中,在该系统里输入输出块(IOB)必须频繁设置为三态

Clock Event1: T1、T2 和 T4 被拉低以释放三态条件。OSERDESE2 中 T1 - T4 和 D1 - D4 的串行化路径相同(包括延迟),这样在Clock Event1 期间,bit EFGH 总是与 T1 - T4 引脚上呈现的 0010 对齐。

Clock Event2:在 EFGH 被采样到 OSERDESE2 中一个 CLK 周期后,数据bit E 出现在 OQ 端。 此延迟与上表中列出的 4:1 DDR 模式 OSERDESE2 一个 CLK 周期的延迟一致。 在Clock Event1 期间 T1 处的三态比特 0,在 0010 被采样到 OSERDESE2 三态模块中一个 CLK 周期后出现在 TQ 端。

6 总结

本篇详细描述了OSERDESE2并串转换器的原语,对属性和输入输出端口已经工作的时序和扩展模式均进行了详细的说明,下一篇,我们对OSERDESE2原语进行仿真,方便大家从时序图和实际配置上熟悉这个原语的用法,敬请期待!!!