第一章 前言

在电力电子领域,功率器件是电能变换的核心,直接决定了电源系统的效率、功率密度和可靠性。传统硅(Si)基 MOSFET 经过数十年发展,已逼近材料物理极限:开关速度受限、反向恢复损耗大、高温下特性劣化严重,难以满足当下快充、数据中心、新能源汽车、储能等场景对高频、高效、高功率密度的核心需求。

以氮化镓(GaN)为代表的第三代宽禁带半导体,凭借材料本身的颠覆性优势,成为功率器件的主流发展方向,而 GaN HEMT(高电子迁移率晶体管)正是 GaN 功率器件的核心实现形式。

1.1 宽禁带半导体的核心优势

半导体的禁带宽度直接决定了器件的击穿场强、工作温度、开关速度等核心特性,核心材料对比如下:

| 材料特性 | 硅(Si) | 氮化镓(GaN) | 碳化硅(SiC) |

|---|---|---|---|

| 禁带宽度(eV) | 1.12 | 3.4 | 3.26 |

| 击穿场强(MV/cm) | 0.3 | 3.3 | 2.5 |

| 电子饱和漂移速度(×10⁷cm/s) | 1.0 | 2.5 | 2.0 |

| 电子迁移率(cm²/V・s) | 1350 | 2000(2DEG) | 900 |

| 热导率(W/m・K) | 150 | 130(GaN 本体)/ 490(SiC 衬底) | 490 |

1.2 GaN HEMT 的核心差异化优势

- 极低的开关损耗:无传统 Si MOS 的体二极管,反向恢复电荷 Qrr≈0,开关速度可达 ns 级,高频下损耗远低于 Si 器件,可将开关频率提升 10 倍以上,大幅缩小磁性元件体积。

- 极低的导通损耗:异质结形成的二维电子气(2DEG)具有超高电子迁移率,相同耐压和芯片面积下,导通电阻 Rds (on) 仅为 Si MOS 的 1/5~1/3。

- 优异的高温特性:宽禁带带来更高的本征载流子激发温度,工作结温可达 150℃~175℃,且导通电阻的温度系数远低于 Si 器件,高温下特性劣化极小。

- 高功率密度:高频 + 高效的特性,可使电源系统的功率密度提升 3~5 倍,完美契合消费类快充、车载 OBC、服务器电源的小型化需求。

1.3 本文核心内容框架

本文将按照【基础认知→内部结构→分类与工作原理→电气特性→参数详解与计算→损耗分析→选型方法→典型应用→设计避坑】的逻辑,由浅入深完成全链路讲解,确保读者从理论到工程实现全面掌握 GaN HEMT。

第二章 GaN HEMT 的基础认知与核心内部结构

想要吃透 GaN HEMT 的工作原理,必须先理解其核心结构与导电沟道的形成机制 ------ 这是 GaN HEMT 与传统 Si MOSFET 最本质的区别。

2.1 什么是 HEMT?

HEMT 全称高电子迁移率晶体管(High Electron Mobility Transistor) ,也被称为调制掺杂场效应晶体管(MODFET),核心是利用两种不同禁带宽度的半导体材料形成异质结,在异质结界面处产生高迁移率的二维电子气(2DEG)作为导电沟道,通过栅极电压控制 2DEG 的浓度,实现对器件通断的控制。

与传统 Si MOSFET 的核心差异:

- Si MOSFET 的导电沟道是栅极电压诱导形成的反型层,电子迁移率受晶格散射影响大,且必须施加栅极电压才能形成沟道;

- GaN HEMT 的导电沟道是异质结极化效应自发形成的 2DEG,电子被限制在极薄的势阱中,几乎不受晶格散射,迁移率极高,且沟道可在零栅压下存在。

2.2 极化效应:GaN HEMT 导电沟道的核心成因

GaN HEMT 的 2DEG 形成,完全依赖于 GaN 材料的自发极化 和压电极化效应,这是整个器件的物理基础。

- 自发极化:GaN 和 AlGaN 均为纤锌矿晶体结构,晶格本身具有不对称性,会自发产生固定的极化电荷,极化方向沿晶体 c 轴方向。

- 压电极化:AlGaN 与 GaN 的晶格常数存在差异,AlGaN 层生长在 GaN 层上时会产生晶格应变,应变会诱导产生额外的极化电荷,与自发极化电荷叠加。

两种极化效应叠加后,会在 AlGaN/GaN 异质结的界面处,GaN 一侧感应出大量的正电荷,这些电荷吸引自由电子聚集在界面处极薄(<10nm)的量子势阱中,形成二维电子气(2DEG)------ 这就是 GaN HEMT 的天然导电沟道。

2.3 GaN HEMT 的内部层叠结构详解

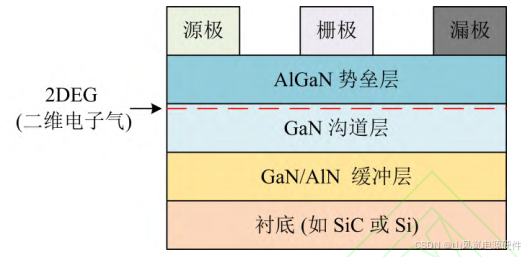

主流 GaN HEMT 均为横向结构,从下到上的核心层叠结构如下,每一层都有明确的功能定位:

- 衬底层

- 核心作用:为 GaN 外延层提供机械支撑,主流衬底分为三类:硅(Si)衬底、碳化硅(SiC)衬底、蓝宝石衬底。

- 主流方案:650V 消费级 / 工业级器件几乎均采用Si 衬底,成本低、可兼容硅基晶圆产线;高功率、高频射频器件采用 SiC 衬底,热导率更高、晶格失配更小。

- 缓冲层

- 核心作用:缓解衬底与 GaN 层之间的晶格失配和热失配,减少位错缺陷,同时阻断漏极到衬底的漏电,提升器件击穿电压。

- 主流方案:采用 AlGaN/AlN 渐变缓冲层结构,厚度可达数微米。

- GaN 沟道层

- 核心作用:异质结的低禁带一侧,是 2DEG 的形成区域,器件的导电沟道就位于该层与 AlGaN 势垒层的界面处。

- 特性:本征 GaN 材料,厚度约 100~200nm,电子迁移率极高。

- AlN 插入层

- 核心作用:隔离 AlGaN 势垒层与 GaN 沟道层,减少合金散射,进一步提升 2DEG 的电子迁移率,厚度仅 1~2nm。

- AlGaN 势垒层

- 核心作用:异质结的高禁带一侧,与 GaN 沟道层形成异质结,通过极化效应产生 2DEG,是决定器件阈值电压、沟道浓度的核心层。

- 特性:Al 组分通常在 15%~25%,厚度约 20~30nm,厚度和 Al 组分直接决定极化电荷的密度。

- 栅极、源极、漏极

- 源极 / 漏极:与 2DEG 形成欧姆接触,电阻极低,通常采用 Ti/Al/Ti/Au 多层金属结构,位于器件两端。

- 栅极:位于源极和漏极之间,与 AlGaN 势垒层形成肖特基接触或 MIS(金属 - 绝缘层 - 半导体)接触,通过施加栅极电压控制 2DEG 的浓度,实现器件的通断控制。

2.4 二维电子气(2DEG)的核心特性

- 超高电子迁移率:室温下迁移率可达 1500~2000 cm²/V・s,远高于 Si 体材料的 1350 cm²/V・s,且在高电场下仍能保持高漂移速度,导通损耗极低。

- 极高的电子浓度:面密度可达 1×10¹³ cm⁻² 以上,且仅存在于界面极薄的势阱中,沟道电阻极小。

- 二维限制特性:电子被限制在垂直于界面的一维势阱中,只能在平行于界面的平面内自由移动,几乎不受晶格散射和杂质散射影响,开关速度极快。

第三章 GaN HEMT 的分类与工作原理

基于上述核心结构,GaN HEMT 根据零栅压下的沟道状态、栅极结构、实现形式,形成了不同的器件分类,其中 耗尽型(D-mode)与增强型(E-mode)是最核心的分类,直接决定了器件的工作原理和应用场景。

3.1 核心分类:耗尽型(D-mode)vs 增强型(E-mode)

| 特性 | 耗尽型(D-mode,常通型) | 增强型(E-mode,常断型) |

|---|---|---|

| 零栅压(Vgs=0V)状态 | 2DEG 存在,器件导通 | 2DEG 被耗尽,器件关断 |

| 阈值电压 Vth | 负值(通常 - 3V~-10V) | 正值(通常 1V~2V) |

| 导通条件 | Vgs > Vth(负压关断,零压 / 正压导通) | Vgs > Vth(正压导通,零压 / 负压关断) |

| 电源系统适配性 | 需负压关断,上电易直通,不适合直接用于功率变换 | 零压关断,与 Si MOS 逻辑一致,适配主流电源拓扑 |

3.2 耗尽型 D-mode GaN HEMT 的工作原理

D-mode 是 GaN HEMT 的原生结构,零栅压下,AlGaN/GaN 异质结的极化效应已形成高浓度 2DEG,源漏之间形成低阻导电沟道,器件处于导通状态。

- 关断过程:当栅极施加负压(Vgs < Vth),栅极的负电压会在异质结界面处产生垂直向下的电场,耗尽界面处的 2DEG,沟道电阻急剧上升,器件进入关断状态。

- 导通过程:当栅极负压消失(Vgs=0V)或施加正压,耗尽效应消失,2DEG 恢复,器件重新导通。

核心局限:常通特性不符合功率电源的安全要求,上电时若栅极驱动未就绪,器件处于导通状态,极易造成母线短路炸机,因此极少单独使用,主要用于级联型 Cascode GaN 结构。

3.3 增强型 E-mode GaN HEMT 的主流实现技术与工作原理

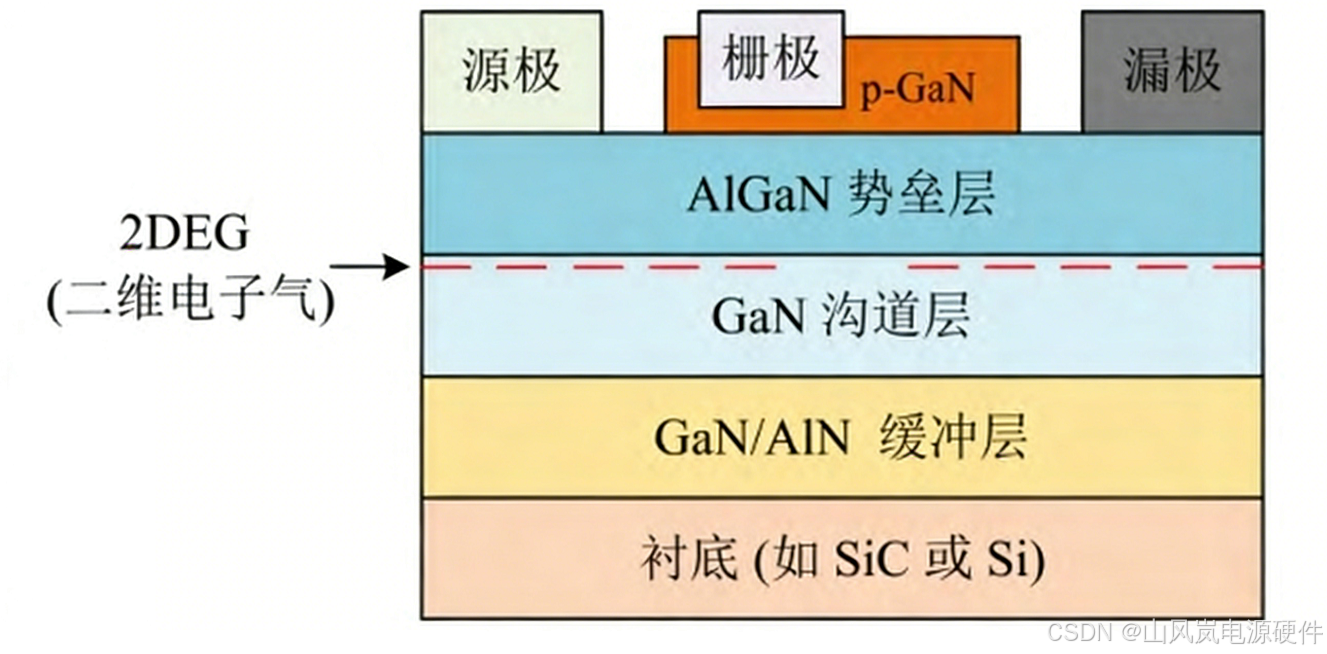

E-mode(常断型)是功率电源应用的主流方案,核心设计目标是:零栅压下耗尽 2DEG,使器件处于关断状态,仅当 Vgs 超过正的阈值电压时,沟道才会形成并导通。目前主流的实现技术有 3 种,其中 p-GaN 栅技术占比超 90%。

3.3.1 p-GaN 栅技术(主流)

- 结构改动:在 AlGaN 势垒层与栅极之间,增加一层 p 型掺杂的 GaN 层(p-GaN)。

- 工作原理 :

- 零栅压(Vgs=0V)时,p-GaN 层与 AlGaN 势垒层形成的 PN 结产生内建电场,该电场会抵消极化效应产生的电场,耗尽异质结界面处的 2DEG,沟道被阻断,器件处于关断状态;

- 当栅极施加正向电压(Vgs > Vth,通常 + 4V~+6V),PN 结正偏,内建电场被抵消,极化效应恢复,界面处重新形成 2DEG,器件导通。

- 优势:工艺成熟、阈值电压稳定性好、漏电低,是纳微、英诺赛科、GaN Systems、TI 等主流厂商的核心方案。

3.3.2 凹槽栅(Recessed Gate)技术

- 结构改动:通过刻蚀工艺,将栅极下方的 AlGaN 势垒层部分刻蚀减薄,甚至刻穿至 GaN 沟道层。

- 工作原理:AlGaN 势垒层的厚度直接决定极化电荷的密度,减薄后零栅压下的极化效应不足以形成 2DEG,沟道被耗尽,器件关断;当施加正向栅极电压时,诱导形成 2DEG,器件导通。

- 优势:工艺简单,栅极漏电低;劣势:刻蚀精度要求极高,阈值电压一致性难控制,商用应用较少。

3.3.3 氟离子注入技术

- 结构改动:在栅极下方的 AlGaN 势垒层中注入带负电的氟离子。

- 工作原理:氟离子的负电荷会产生反向电场,抵消极化效应,零栅压下耗尽 2DEG,实现常断特性;正向栅压可抵消氟离子的电场,恢复 2DEG,实现导通。

- 优势:阈值电压可调范围大;劣势:高温下氟离子易扩散,器件长期可靠性差,商用极少。

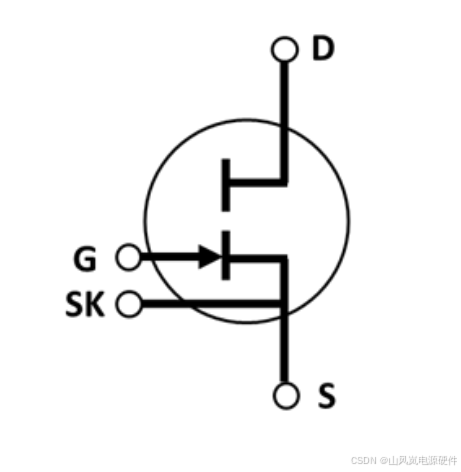

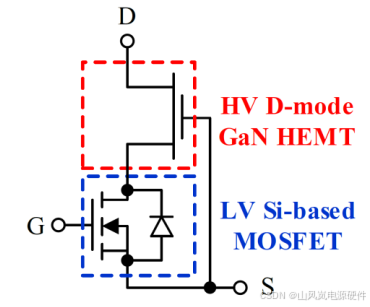

3.4 级联型 Cascode GaN HEMT 的结构与工作原理

Cascode 结构是解决 D-mode GaN 应用难题的经典方案,也是工业级 GaN 器件的主流形式,完美兼顾了 GaN 的性能与 Si MOS 的驱动兼容性。

- 结构组成 :将一颗 ** 耗尽型 D-mode GaN HEMT(高压、大电流)与一颗 低压增强型 Si MOSFET(耐压 30V~100V,极低 Rds (on))** 进行共源共栅级联:

- Si MOS 的漏极接 D-mode GaN 的源极;

- Si MOS 的源极与 D-mode GaN 的源极共地;

- D-mode GaN 的栅极直接接 Si MOS 的源极(即 Vgs (GaN)=0V);

- 整个器件的栅极是 Si MOS 的栅极,漏极是 D-mode GaN 的漏极。

- 工作原理 :

- 关断状态:Si MOS 的 Vgs=0V,Si MOS 关断,D-mode GaN 的源极电位被抬高,其 Vgs= -Vds (Si),负压超过 D-mode GaN 的阈值电压,GaN 器件关断,承受高压母线电压;

- 导通状态:Si MOS 的 Vgs 施加 + 10V~+15V 驱动电压,Si MOS 导通,D-mode GaN 的 Vgs=0V,恢复原生导通状态,整个器件导通,导通电阻为 GaN 的 Rds (on)+Si MOS 的 Rds (on)(Si MOS 的 Rds (on) 极低,可忽略)。

- 核心优劣势 :

- 优势:驱动逻辑与 Si MOS 完全兼容,可直接替换 Si MOS,无需专用驱动电路,无栅极过压击穿风险,工业级可靠性高,是 Transphorm、安森美、ST 等厂商的主流方案;

- 劣势:存在低压 Si MOS 的体二极管,有极小的反向恢复电荷,开关速度略低于单片 E-mode GaN,封装体积更大。

3.5 其他分类方式

- 按耐压等级分类 :

- 低压 GaN:耐压≤200V,主要用于 POL 电源、DCDC 模块、激光雷达、电机驱动;

- 中压 GaN:耐压 600V~650V,主流消费级 / 工业级器件,用于快充、图腾柱 PFC、LLC 电源、车载 OBC;

- 高压 GaN:耐压≥1200V,用于光伏逆变器、储能 PCS、工业变频器。

- 按栅极结构分类:肖特基栅 HEMT、MIS 栅 HEMT、p-GaN 栅 HEMT。

- 按集成度分类:分立 GaN 器件、GaN IC(驱动 + GaN 管集成)、全集成 GaN 功率模块(控制器 + 驱动 + GaN 半桥)。

第四章 GaN HEMT 的核心电气特性详解

基于上述结构与工作原理,GaN HEMT 的电气特性与传统 Si MOSFET 存在本质差异,掌握这些特性是器件应用的核心前提。

4.1 静态输出特性(Id-Vds)

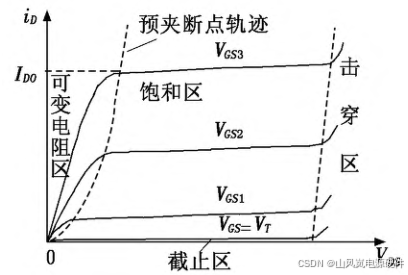

输出特性描述的是栅源电压 Vgs 固定时,漏极电流 Id 与漏源电压 Vds 的关系,分为三个工作区域:

- 线性区(欧姆区):Vds 较小时,Id 与 Vds 呈线性关系,沟道电阻恒定,器件相当于一个受 Vgs 控制的可变电阻,Vgs 越大,2DEG 浓度越高,沟道电阻越小,斜率越大。

- 饱和区:当 Vds 增大到饱和电压后,Id 不再随 Vds 增大而上升,进入恒流状态,此时沟道被夹断,Id 仅由 Vgs 决定,跨导 gfs 恒定,该区域是器件线性放大的工作区,功率开关应用中仅在开关瞬态经过。

- 击穿区:当 Vds 超过器件的击穿电压 BVdss 时,漏极电流急剧上升,器件进入雪崩击穿,永久损坏。

与 Si MOS 的核心差异:GaN HEMT 的饱和区 Id 随 Vds 的上升更平缓,输出阻抗更高,且线性区的导通电阻远低于同规格 Si MOS。

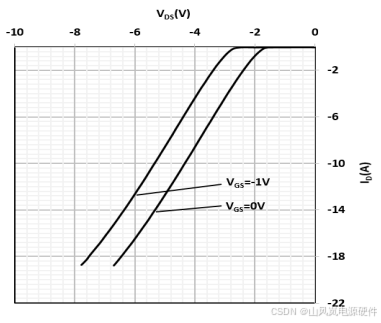

4.2 转移特性(Id-Vgs)与跨导特性

- 转移特性 :描述漏源电压 Vds 固定时,漏极电流 Id 与栅源电压 Vgs 的关系 ,是器件阈值电压、跨导的核心表征曲线。

- 对于 E-mode GaN:当 Vgs <Vth 时,Id≈0,器件关断;当 Vgs> Vth 时,Id 随 Vgs 的增大呈指数上升,进入导通状态。

- 核心特点:主流 p-GaN 栅 GaN 的 Vth 通常为 1.0V~2.0V,推荐驱动电压为 + 4.5V~+5.5V,最大允许 Vgs 仅为 + 6V 左右,电压窗口极窄,这是驱动设计的核心要点。

- 跨导特性:跨导 gfs=ΔId/ΔVgs,表征栅极电压对漏极电流的控制能力,GaN HEMT 的 2DEG 浓度随 Vgs 变化极快,因此跨导远高于 Si MOS,开关速度更快,控制灵敏度更高。

4.3 第三象限反向导通特性(GaN 最核心的差异化特性)

这是 GaN HEMT 与 Si MOSFET 最本质的区别,也是电源设计中最容易踩坑的点:GaN HEMT 无传统的体二极管,不存在 PN 结正向导通的反向恢复过程。

- 反向导通机制:当器件处于关断状态(Vgs <Vth),且漏源电压 Vds 为负(源极电位高于漏极)时,若 | Vds|> |Vgs - Vth|,沟道会被反向开启,电子从源极流向漏极,形成反向导通电流。

- 反向导通压降:Vsd = -(Vgs - Vth),完全由栅极电压和阈值电压决定,与反向电流大小几乎无关。例如:Vgs=0V,Vth=1.5V 时,反向导通压降 Vsd≈1.5V,远高于 Si MOS 体二极管的 0.7V 正向压降。

- 核心特性 :反向导通是沟道导通,而非 PN 结导通,因此反向恢复电荷 Qrr≈0,开关速度极快,无反向恢复损耗;但反向导通压降较高,死区时间内的反向导通损耗不可忽视,高频下占比极高。

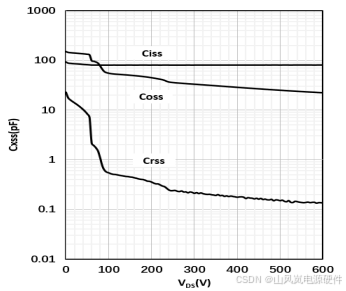

4.4 电容特性与开关速度的关联

GaN HEMT 的电容特性直接决定了开关速度、驱动损耗和 EMI 特性,与 Si MOS 一样,分为三类电容:

- 输入电容 Ciss = Cgs + Cgd:栅极与源极、栅极与漏极的电容之和,决定了栅极驱动的充电时间,Ciss 越小,开关速度越快,驱动损耗越小。

- 输出电容 Coss = Cds + Cgd:漏极与源极、漏极与栅极的电容之和,决定了器件关断后的电压上升时间,Coss 越小,关断损耗越小。

- 反向传输电容 Crss = Cgd:也叫米勒电容,是栅极与漏极之间的电容,决定了米勒平台的时长,Crss 越小,米勒效应越弱,开关速度越快,越不容易发生误开通。

与 Si MOS 的核心差异:GaN HEMT 的 Crss 极小,仅为同规格 Si MOS 的 1/10~1/5,米勒效应极弱,开关速度可达 ns 级,这是其高频低损耗的核心原因;同时,GaN 的电容均为非线性电容,随 Vds 的增大急剧下降,工程计算中需采用有效值而非额定值。

4.5 温度特性:GaN 对比 Si 的核心优势

- 导通电阻温度特性:GaN HEMT 的 Rds (on) 温度系数约为 0.1%/℃~0.15%/℃,仅为 Si MOS 的 1/2,150℃结温下,Rds (on) 仅上升 20% 左右,而 Si MOS 会上升 50% 以上,高温下导通损耗优势显著。

- 阈值电压温度特性:GaN 的 Vth 具有负温度系数,约为 - 0.5mV/℃~-1mV/℃,温度升高时 Vth 略有下降,需注意高温下的误开通风险,但系数远低于 Si MOS,并联均流特性更好。

- 漏电流特性:宽禁带特性使 GaN 的本征载流子浓度极低,高温下漏极漏电流 Idss 远小于 Si MOS,高温可靠性更高。

第五章 GaN HEMT 关键参数全解析与工程计算方法

器件 datasheet 中的参数是设计选型的核心依据,本章将对 GaN HEMT 的核心参数进行分类详解,同时给出工程化的计算方法,所有公式均可直接用于电源设计校核。

5.1 极限参数:定义、物理意义与设计校核

极限参数是器件的绝对额定值,设计中任何情况下都不能超过,否则会造成器件永久损坏。

| 参数符号 | 参数名称 | 定义与物理意义 | 工程校核方法 |

|---|---|---|---|

| BVdss | 漏源击穿电压 | 栅源短路(Vgs=0V)时,器件漏极与源极之间的最大击穿电压,决定器件的耐压等级 | 设计中,器件工作时的最大 Vds 尖峰必须≤80%×BVdss,预留 20% 以上的降额余量;例如 650V GaN,最大工作尖峰不得超过 520V |

| Vgs(max) | 栅源最大电压 | 栅极与源极之间允许施加的最大正向 / 反向电压,p-GaN 栅 GaN 通常为 + 6V/-10V | 驱动电路设计中,必须确保 Vgs 的正向过冲≤+5.5V,反向负压≤-8V,严禁超过额定值,否则栅极会瞬间击穿 |

| Id(max) | 连续漏极电流 | 壳温 25℃/100℃时,器件能够持续承受的最大漏极直流电流 | 设计中,器件工作的连续漏极电流有效值必须≤70%×Id (max)@100℃,预留足够的降额余量 |

| Idm | 脉冲漏极电流 | 器件能够承受的最大脉冲漏极电流,由器件的键合线、芯片电流密度决定 | 设计中,拓扑的峰值漏极电流必须≤Idm,避免脉冲过流损坏器件 |

| Tj(max) | 最大结温 | 器件芯片能够承受的最高结温,商用器件通常为 150℃或 175℃ | 设计中,最坏工况下的器件结温必须≤90%×Tj (max),例如 150℃结温的器件,最高工作结温不得超过 135℃ |

| EAS | 单脉冲雪崩能量 | 器件能够承受的单次雪崩击穿能量,表征器件的雪崩耐量 | GaN HEMT 的雪崩耐量远低于 Si MOS,设计中严禁让器件工作在雪崩状态,必须通过钳位、缓冲电路抑制电压尖峰 |

5.2 直流参数:定义、测试条件与工程计算

直流参数决定了器件的导通损耗和静态特性,所有参数均有对应的测试条件,设计中必须根据实际工况进行修正。

| 参数符号 | 参数名称 | 定义与物理意义 | 工程计算与修正 |

|---|---|---|---|

| Vth | 阈值电压 | 器件开始导通时的栅源电压,E-mode GaN 为正值,通常 1.0V~2.0V | 高温下 Vth 会下降,设计中需按最高结温下的最小 Vth 校核误开通风险,确保关断时 Vgs <Vth (min)@Tj (max) |

| Rds(on) | 导通电阻 | 器件导通时,漏极与源极之间的通态电阻,是决定导通损耗的核心参数 | 1. 导通损耗计算公式:P_cond = I_d(rms)² × Rds(on)@Tj;2. 温度修正:Rds(on)@Tj = Rds(on)@25℃ × [1 + α×(Tj - 25℃)],其中 α 为温度系数,通常 0.1%/℃~0.15%/℃ |

| gfs | 正向跨导 | 漏极电流变化量与栅源电压变化量的比值,表征栅极对漏极电流的控制能力 | 用于计算器件的导通压降:Vds(on) = I_d × Rds(on) + I_d / gfs,大电流下跨导决定了导通压降的增量 |

| Idss | 漏源截止漏电流 | 器件关断时,漏极与源极之间的漏电流,Vgs=0V、Vds=BVdss 时测试 | 截止损耗计算公式:P_off = Vds × Idss@Tj,高温下 Idss 会上升,需按最高结温校核 |

| Igss | 栅源漏电流 | 栅极与源极之间的漏电流,表征栅极的绝缘性能 | 用于校核驱动电路的驱动能力,确保驱动电流远大于 Igss,避免栅极电压漂移 |

5.3 开关参数:定义、损耗关联与定量计算

开关参数决定了器件的开关损耗、开关速度和驱动设计要求,是 GaN 高频应用的核心参数。

| 参数符号 | 参数名称 | 定义与物理意义 | 工程计算与应用 |

|---|---|---|---|

| td(on) | 开通延迟时间 | 从栅极驱动电压上升到 10% Vgs,到漏极电流上升到 10% Id 的时间 | 用于死区时间设计,死区时间必须大于 td (on),避免上下管直通 |

| tr | 电流上升时间 | 漏极电流从 10% Id 上升到 90% Id 的时间,决定开通损耗的大小 | 开通损耗与 tr 正相关,tr 越短,开通速度越快,开通损耗越小 |

| td(off) | 关断延迟时间 | 从栅极驱动电压下降到 90% Vgs,到漏极电流下降到 90% Id 的时间 | 死区时间设计必须大于 td (off),同时需结合反向导通特性优化 |

| tf | 电流下降时间 | 漏极电流从 90% Id 下降到 10% Id 的时间,决定关断损耗的大小 | tf 越短,关断速度越快,关断损耗越小,但电压尖峰越高,需平衡 |

| Qg | 总栅极电荷 | 驱动器件开通所需的总栅极电荷,决定驱动损耗的大小 | 1. 驱动损耗计算公式:P_gate = Qg × Vgs × f_sw;2. 驱动电流计算:I_gate = Qg / t_rise,用于匹配驱动芯片的驱动能力 |

| Qgs | 栅源电荷 | 栅极与源极之间的充电电荷,决定开通延迟时间 | Qgs 越小,开通延迟越短,开关速度越快 |

| Qgd | 栅漏电荷(米勒电荷) | 米勒平台阶段的充电电荷,决定米勒平台的时长 | Qgd 越小,米勒效应越弱,开关速度越快,越不容易发生误开通,GaN 的 Qgd 远小于 Si MOS |

| Eon | 单次开通损耗 | 器件单次开通过程中消耗的能量,datasheet 中通常给出固定测试条件下的数值 | 1. 总开通损耗:P_on = Eon × f_sw;2. 实际工况修正:Eon 与母线电压、漏极电流、栅极电阻正相关,需根据实际工况按比例修正 |

| Eoff | 单次关断损耗 | 器件单次关断过程中消耗的能量 | 1. 总关断损耗:P_off = Eoff × f_sw;2. 关断损耗与母线电压、漏极电流正相关,与栅极电阻负相关 |

5.4 热参数:热阻模型与结温计算

热参数决定了器件的散热能力和最高工作结温,是可靠性设计的核心。

-

核心热参数

- Rth (jc):结到壳的热阻,单位℃/W,表征芯片到器件封装外壳的导热能力,由芯片尺寸、封装形式决定,数值越小,导热能力越强。

- Rth (ca):壳到环境的热阻,单位℃/W,表征器件外壳到环境空气的导热能力,由散热器、散热风道决定。

- Rth (ja):结到环境的热阻,单位℃/W,Rth (ja)=Rth (jc)+Rth (ca),表征无散热器时,芯片到环境的总导热能力。

-

结温工程计算公式

Tj = P_total × (Rth(jc) + Rth(ca)) + Ta

其中:

- Tj:器件工作结温(℃);

- P_total:器件的总损耗(W),包括导通损耗、开关损耗、驱动损耗、截止损耗、死区损耗;

- Ta:环境温度(℃);

- 设计校核:最坏工况下(最高环境温度、最大负载),Tj 必须≤90%×Tj (max)。

5.5 可靠性参数

- ESD:静电放电耐量,GaN HEMT 的栅极氧化层极薄,ESD 耐量远低于 Si MOS,通常为 ±2kV(人体模型),生产和焊接过程中必须做好静电防护。

- HTGB:高温栅偏置寿命,表征器件栅极的长期可靠性,是评估器件寿命的核心参数。

- HTRB:高温反偏寿命,表征器件高压关断状态下的长期可靠性,决定器件的使用寿命。

第六章 GaN HEMT 开关过程与损耗精细化分析

GaN HEMT 的核心优势是高频低损耗,而损耗的核心来源是开关过程,本章将分阶段拆解开关瞬态过程,精细化分析各类损耗的成因与计算方法,为效率优化提供理论依据。

6.1 开通瞬态过程分阶段详解

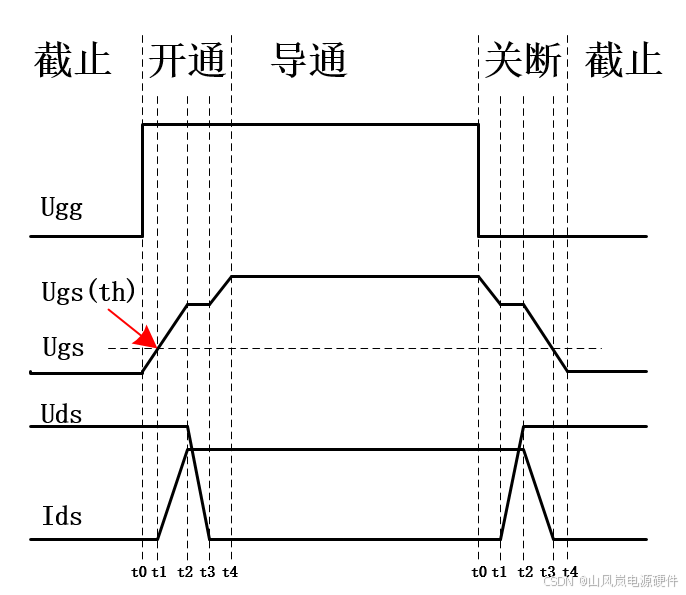

E-mode GaN HEMT 的开通过程分为 4 个阶段,全程仅需数 ns~ 数十 ns,远快于 Si MOS:

- 阶段 1:开通延迟阶段(t0-t1)

- 过程:栅极驱动电压开始上升,对栅源电容 Cgs 充电,Vgs 从 0V 上升到阈值电压 Vth;

- 电气状态:漏极电流 Id=0,漏源电压 Vds = 母线电压 Vbus,器件仍处于关断状态;

- 损耗:无功率损耗,仅驱动电路对 Cgs 充电,产生驱动损耗。

- 阶段 2:电流上升阶段(t1-t2)

- 过程:Vgs 从 Vth 上升到米勒平台电压 Vgp,栅极继续对 Cgs 充电,2DEG 浓度逐渐升高,沟道逐渐导通;

- 电气状态:Id 从 0 上升到负载电流 Io,Vds 仍保持 Vbus 不变;

- 损耗:Vds=Vbus,Id 持续上升,产生显著的开通损耗,是开通损耗的主要来源。

- 阶段 3:米勒平台阶段(t2-t3)

- 过程:Vgs 保持米勒平台电压 Vgp 不变,驱动电流全部用于对米勒电容 Cgd 充电,漏极电压开始下降;

- 电气状态:Id 保持 Io 不变,Vds 从 Vbus 下降到导通压降 Vds (on);

- 损耗:Id=Io,Vds 持续下降,产生开通损耗,GaN 的 Cgd 极小,米勒平台时长仅为 Si MOS 的 1/10,该阶段损耗远低于 Si MOS。

- 阶段 4:导通稳态阶段(t3-t4)

- 过程:Vds 下降到 Vds (on),米勒效应结束,驱动电压继续上升到额定驱动电压 + 5V,对 Cgs 和 Cgd 完成充电;

- 电气状态:器件完全导通,Id=Io,Vds=Vds (on);

- 损耗:仅导通损耗,无开关损耗。

6.2 关断瞬态过程分阶段详解

关断过程是开通过程的逆过程,同样分为 4 个阶段:

- 阶段 1:关断延迟阶段(t0-t1)

- 过程:栅极驱动电压从 + 5V 开始下降,Cgs 和 Cgd 通过驱动电路放电,Vgs 下降到米勒平台电压 Vgp;

- 电气状态:器件仍处于完全导通状态,Id=Io,Vds=Vds (on);

- 损耗:无开关损耗,仅驱动放电损耗。

- 阶段 2:电压上升阶段(t1-t2)

- 过程:Vgs 保持 Vgp 不变,米勒电容 Cgd 放电,Vds 从 Vds (on) 上升到母线电压 Vbus;

- 电气状态:Id 保持 Io 不变,Vds 持续上升;

- 损耗:Id=Io,Vds 持续上升,产生关断损耗,是关断损耗的主要来源。

- 阶段 3:电流下降阶段(t2-t3)

- 过程:Vds 达到 Vbus 后,米勒效应结束,Vgs 从 Vgp 下降到 Vth,Cgs 继续放电,2DEG 逐渐被耗尽;

- 电气状态:Id 从 Io 下降到 0,Vds 保持 Vbus 不变;

- 损耗:Vds=Vbus,Id 持续下降,产生关断损耗。

- 阶段 4:关断稳态阶段(t3-t4)

- 过程:Vgs 下降到 0V(或负压),器件完全关断,2DEG 被完全耗尽;

- 电气状态:Id=0,Vds=Vbus;

- 损耗:仅极小的截止漏电流损耗,无开关损耗。

6.3 各类损耗的精细化计算与优化方法

6.3.1 导通损耗

- 计算公式:

P_cond = I_d(rms)² × Rds(on)@Tj

- 影响因素:漏极电流有效值、导通电阻、结温;

- 优化方法:选择更低 Rds (on) 的器件、优化并联均流、提升散热能力降低结温、优化拓扑降低电流有效值。

6.3.2 开关损耗

-

计算公式 :

P_sw = (Eon + Eoff) × f_sw

-

核心特性:开关损耗与开关频率成正比,这也是 Si MOS 在高频下效率急剧下降的原因;而 GaN 的 Eon 和 Eoff 极小,可在 MHz 级频率下保持高效率。

-

影响因素:母线电压、漏极电流、栅极电阻、开关频率、寄生电感;

-

优化方法:优化栅极驱动电路、减小栅极电阻加快开关速度、优化 PCB 布局减小功率回路寄生电感、采用软开关拓扑(如 LLC、ZVS)完全消除开关损耗。

6.3.3 死区损耗

死区损耗是 GaN 应用中最容易被忽略的损耗,高频下占比可达总损耗的 20% 以上。

-

成因:半桥拓扑中,上下管的死区时间内,续流电流通过关断管的反向沟道导通,GaN 的反向导通压降较高,产生显著的损耗;

-

计算公式 :

P_dead = V_sd × I_sd × t_dead × f_sw

其中,V_sd 为反向导通压降,I_sd 为续流电流有效值,t_dead 为单边死区时间,f_sw 为开关频率; -

优化方法:在保证不直通的前提下,尽可能减小死区时间;优化栅极驱动加快开关速度,缩短死区需求;采用同步整流技术,避免反向续流。

6.3.4 驱动损耗

-

计算公式 :

P_gate = Qg × Vgs × f_sw

-

特性:GaN 的 Qg 极小,驱动损耗远低于同规格 Si MOS,即使在 MHz 级频率下,驱动损耗也可忽略不计。

6.3.5 输出电容损耗

-

成因:器件关断时,母线电压对输出电容 Coss 充电,开通时 Coss 通过沟道放电,产生的损耗;

-

计算公式 :

P_coss = 0.5 × Coss(eff) × Vbus² × f_sw

其中,Coss (eff) 为输出电容的有效值; -

优化方法:选择 Coss 更小的器件,软开关拓扑可消除该损耗。

6.4 GaN 与 Si MOSFET 损耗特性的核心差异

| 损耗类型 | GaN HEMT | Si MOSFET |

|---|---|---|

| 反向恢复损耗 | 无(Qrr≈0) | 大,是高频损耗的主要来源 |

| 开通 / 关断损耗 | 极小,ns 级开关速度 | 大,受米勒效应和反向恢复影响 |

| 死区损耗 | 较高,反向导通压降大 | 较低,体二极管正向压降低 |

| 导通损耗 | 相同规格下更小,高温劣化小 | 更大,高温下 Rds (on) 急剧上升 |

| 驱动损耗 | 极小,Qg 小 | 较大,Qg 大 |

第七章 GaN HEMT 工程化选型方法与避坑指南

掌握了原理、特性和参数计算后,本章将给出可直接落地的 GaN HEMT 选型流程,同时梳理设计中的常见误区与避坑方法,避免选型失误导致的炸机、效率低等问题。

7.1 GaN HEMT 选型的核心流程

完整的选型流程分为 7 步,环环相扣:

确定拓扑与应用场景 → 确定耐压等级 → 确定电流等级 → 导通与开关特性权衡 → 驱动兼容性选型 → 封装与热设计选型 → 可靠性校核

7.2 步骤 1:基于拓扑与应用场景的器件选型原则

不同的拓扑和应用场景,对 GaN 器件的需求存在本质差异,选型前必须明确核心需求

7.3 步骤 2:耐压等级的定量选型计算

耐压选型的核心原则是:预留足够的降额余量,避免器件进入雪崩状态。

定量计算公式:

BVdss ≥ Vds_max_peak / 0.8

其中,Vds_max_peak 为器件工作时的最大漏源电压尖峰,0.8 为 20% 的降额系数,恶劣工况下需提升至 0.7(30% 降额)。

7.4 步骤 3:电流等级的定量选型计算

电流选型需同时校核连续电流有效值 和峰值脉冲电流,双维度满足要求。

-

连续电流有效值校核 :

Id(max)@100℃ ≥ I_d(rms)_max / 0.7

其中,I_d (rms)_max 为最坏工况下的漏极电流有效值,0.7 为 30% 的降额系数,必须采用 100℃壳温下的 Id (max),而非 25℃的额定值。 -

峰值脉冲电流校核 :

Idm ≥ I_d(pk)_max

其中,I_d (pk)_max 为拓扑的最大漏极峰值电流,例如反激拓扑的峰值电流计算公式:I_d(pk) = 2 × Pout / (Vin(min) × η)

-

注意事项:GaN 器件的芯片面积通常小于 Si MOS,脉冲电流耐量更低,严禁超额定峰值电流工作,否则会烧毁键合线和芯片。

7.5 步骤 4:导通电阻与开关特性的权衡选型

Rds (on) 和 Qg 是 GaN 器件选型的核心权衡点,二者呈正相关:芯片面积越大,Rds (on) 越小,但 Qg 和 Coss 越大,开关损耗越大。

- 低频应用(f_sw < 100kHz):导通损耗占主导,优先选择更低 Rds (on)的器件,无需过度关注 Qg;

- 中频应用(100kHz < f_sw < 500kHz):需平衡导通损耗和开关损耗,选择 Rds (on) 和 Qg 综合最优的器件;

- 高频应用(f_sw > 500kHz) :开关损耗占主导,优先选择更低 Qg、更小 Coss的器件,适当牺牲 Rds (on)。

7.6 步骤 5:驱动兼容性与封装选型

- 驱动兼容性选型 :

- 若采用现有 Si MOS 驱动方案,优先选择Cascode GaN,驱动电压 + 10V~+15V,完全兼容;

- 若采用专用 GaN 驱动,选择单片 E-mode GaN,驱动电压 + 4.5V~+5.5V,需选择带欠压锁定、过压保护的专用 GaN 驱动芯片;

- 新手设计优先选择驱动 + GaN 集成的 GaN IC,无需单独设计驱动电路,大幅降低设计难度和炸机风险。

- 封装选型 :

- 消费类快充:优先选择 DFN5*6*、*DFN8*8封装,体积小、寄生电感小、散热性能好;

- 工业级电源:优先选择 TO-220、TO-247、D2PAK 封装,散热性能好,易于安装散热器;

- 高频大电流应用:优先选择 LGA、QFN 封装,寄生电感极小,开关速度快,EMI 特性好。

7.7 选型常见误区与踩坑点规避

- 误区 1:只看耐压和 Rds (on),忽略 Vgs 额定值

- 坑点:E-mode GaN 的 Vgs 最大额定值仅 + 6V,用 Si MOS 的 12V 驱动会直接击穿栅极;

- 规避:选型时必须先确认 Vgs 额定范围,匹配对应的驱动芯片,驱动电路增加栅极过压保护。

- 误区 2:忽略第三象限反向导通特性,死区时间设置过大

- 坑点:死区时间过大,反向续流时间长,死区损耗急剧上升,效率大幅下降,甚至器件过热损坏;

- 规避:选型时关注反向导通压降,根据器件的开关速度设置最小可行死区时间。

- 误区 3:照搬 Si MOS 的降额规则,忽略 GaN 的雪崩耐量

- 坑点:GaN 的雪崩耐量远低于 Si MOS,按 Si MOS 的 80% 降额,电压尖峰超标会导致器件雪崩击穿;

- 规避:耐压降额≥20%,恶劣工况下降额≥30%,优化 PCB 布局和缓冲电路抑制电压尖峰,严禁器件工作在雪崩状态。

- 误区 4:只看 25℃的 Rds (on),忽略高温特性

- 坑点:高温下 Rds (on) 上升,导通损耗超标,器件过热;

- 规避:必须按最高工作结温下的 Rds (on) 进行损耗计算和选型。

第八章 主流 GaN HEMT 器件类型与典型设计应用

本章将梳理市面主流的 GaN 厂商与产品系列,同时结合典型电源拓扑,讲解 GaN HEMT 的工程化应用方案,帮助读者设计。

8.1 市面主流 GaN HEMT 厂商与产品系列

| 厂商 | 核心技术路线 | 主流产品系列 | 典型应用场景 |

|---|---|---|---|

| 纳微半导体(Navitas) | 单片 E-mode p-GaN 栅,GaN IC 集成 | NV61xx、NV62xx 系列(650V) | 消费类快充、高功率密度适配器 |

| 英诺赛科(Innoscience) | 单片 E-mode p-GaN 栅 | INN650D 系列(650V)、INN100K 系列(100V) | 快充、工业电源、车载电源 |

| GaN Systems | 单片 E-mode p-GaN 栅 | GS665xx 系列(650V) | 车载 OBC、储能、服务器电源 |

| 德州仪器(TI) | 单片 E-mode p-GaN 栅,GaN IC 集成 | LMG34xx 系列、LMG35xx 系列 | 图腾柱 PFC、LLC 电源、工业电源 |

| Transphorm | Cascode 级联 GaN | TP65Hxxx 系列(650V)、TP120Hxxx 系列(1200V) | 光伏逆变器、工业电源、车载 OBC |

| 安森美(ON Semiconductor) | Cascode 级联 GaN、E-mode GaN | NTP8G 系列、NVHLxx 系列 | 工业变频器、车载电源、储能 |

| 宜普电源(EPC) | 低压 E-mode GaN | EPC20xx 系列(15V~200V) | 激光雷达、POL 电源、电机驱动 |

8.2 消费类快充:高频 QR 反激变换器应用

QR 反激是消费类快充的主流拓扑,GaN 的应用可将开关频率从传统 Si MOS 的 65kHz 提升到 300kHz~1MHz,磁性元件体积缩小 5 倍以上,实现充电器的小型化。

- 核心设计要点 :

- 器件选型:650V E-mode GaN,优先选择集成驱动的 GaN IC,如纳微 NV6127、英诺赛科 INN650D040A;

- 开关频率:300kHz~1MHz,利用 GaN 无反向恢复的优势,消除 QR 模式的谷底开通损耗;

- 驱动设计:采用专用 5V GaN 驱动,栅极回路长度≤5mm,避免寄生电感导致的振铃;

- 死区时间:优化至 100ns~200ns,大幅减小反向导通损耗。

- 性能提升:65W 快充采用 GaN 方案后,效率可达 94% 以上,功率密度可达 30W/in³ 以上,体积仅为传统 Si 方案的 1/3。

8.3 高效功率因数校正:图腾柱无桥 PFC 应用

传统 Si MOS 的体二极管反向恢复损耗大,无法实现 CCM 模式的图腾柱无桥 PFC,而 GaN 无反向恢复的特性,完美解决了这一难题,图腾柱 PFC 的效率可达 99% 以上,是高效服务器电源、工业电源的主流方案。

- 核心设计要点 :

- 拓扑结构:图腾柱无桥 PFC,高频桥臂采用 GaN HEMT,工频桥臂采用 Si MOS;

- 器件选型:CRM 模式选 650V E-mode GaN,CCM 模式选 Cascode GaN,如 Transphorm TP65H035G4;

- 开关频率:65kHz~200kHz,利用 GaN 的低开关损耗,提升功率密度;

- 核心优势:消除传统桥式 PFC 的二极管导通损耗,功率因数可达 0.999 以上,THD<5%。

8.4 高密度隔离电源:LLC 谐振变换器应用

LLC 谐振变换器是中大功率隔离电源的主流拓扑,可实现 ZVS 零电压开通和 ZCS 零电流关断,完全消除开关损耗,GaN 的应用可将开关频率提升至 500kHz~2MHz,变压器体积大幅缩小。

- 核心设计要点 :

- 器件选型:650V E-mode GaN,优先选择低 Coss、低 Qg 的器件,如 GaN Systems GS66508B;

- 开关频率:500kHz~2MHz,利用 GaN 的超高速开关特性,最大化软开关优势;

- 设计优化:GaN 的输出电容 Coss 极小,可大幅减小 LLC 的励磁电流,降低导通损耗;

- 典型应用:300W~3kW 服务器电源、车载 OBC、工业电源,效率可达 98.5% 以上。

8.5 车载与工业:双向 DCDC 与储能应用

新能源汽车、储能系统对双向 DCDC 变换器的效率、功率密度、可靠性要求极高,GaN 的高频高效特性,可完美契合双向功率变换的需求。

- 核心设计要点 :

- 拓扑结构:双向 Buck/Boost、CLLC 谐振变换器;

- 器件选型:650V/1200V Cascode GaN,驱动兼容性好,工业级可靠性高,如安森美 NTP8G200N;

- 核心优势:双向工作时,无需额外的同步整流管,利用 GaN 的沟道反向导通特性,实现双向高效功率变换,无反向恢复损耗。

8.6 低压大电流:POL 电源与激光雷达应用

低压 GaN HEMT 的开关速度可达亚 ns 级,可实现超高频大电流的功率变换,是 POL 电源、激光雷达、DCDC 模块的核心器件。

- 核心设计要点 :

- 器件选型:100V 以内低压 E-mode GaN,如 EPC EPC2045(100V);

- 开关频率:1MHz~10MHz,可将电感体积缩小至传统 Si 方案的 1/10;

- 典型应用:48V 转 12V 服务器 POL 电源、激光雷达的脉冲驱动电路、大电流 DCDC 模块,效率可达 97% 以上。

第九章 GaN HEMT 工程设计核心注意事项

GaN HEMT 的超高速开关特性,对驱动设计、PCB 布局、热设计、EMI 设计提出了远高于 Si MOS 的要求,本章将讲解设计中的核心规则,避免炸机。

9.1 栅极驱动电路设计关键要点

- 严格控制驱动电压范围:E-mode GaN 的推荐驱动电压为 + 4.5V~+5.5V,最大不得超过 + 6V,负压不得低于 - 10V;驱动电路必须增加稳压管或 TVS 钳位,限制 Vgs 的过冲和负压。

- 匹配合适的栅极电阻 :

- 开通电阻 Rg (on):推荐 2Ω~20Ω,减小 Rg 可加快开通速度,降低开通损耗,但会增大电压尖峰和 EMI;

- 关断电阻 Rg (off):推荐 0Ω~10Ω,小于开通电阻,加快关断速度,避免米勒效应导致的误开通;

- 增加反向并联二极管:关断时通过二极管直接放电,进一步加快关断速度。

- 驱动芯片选型 :优先选择专用 GaN 驱动芯片,要求:

- 驱动电流≥2A,满足 ns 级开关的大电流充放电需求;

- 带欠压锁定(UVLO)功能,确保驱动电压不足时器件保持关断;

- 宽输出电压范围,可输出负压关断,提升抗干扰能力;

- 上升 / 下降时间≤10ns,匹配 GaN 的开关速度。

- 避免误开通 :

- 关断时施加 - 2V~-3V 的负压,大幅提升抗干扰能力,避免米勒效应导致的误开通;

- 栅极与源极之间并联 10kΩ~100kΩ 的下拉电阻,避免栅极悬空导致的误导通。

9.2 PCB 布局布线的核心规则

GaN 的开关速度可达 ns 级,di/dt 高达 100A/ns 以上,极小的寄生电感就会产生巨大的电压尖峰和振铃,PCB 布局是 GaN 设计成败的核心。

- 功率回路最小化原则 :

- 主功率回路(漏极→母线电容→源极)的面积必须最小,长度尽可能短,形成紧凑的环路,减小寄生电感;

- 母线电容必须紧贴器件的漏极和源极引脚,采用高频 MLCC 陶瓷电容,抵消寄生电感的影响。

- 栅极驱动回路最小化原则 :

- 栅极驱动回路(驱动输出→栅极电阻→栅极→源极→驱动地)的长度必须≤5mm,面积最小;

- 驱动回路必须远离功率主回路,避免耦合干扰,导致误开通。

- 接地设计规则 :

- 功率地和信号地必须分开,采用单点接地,避免地弹电压干扰驱动电路;

- 采用 4 层及以上 PCB 设计,内层设置完整的功率地平面和信号地平面,减小寄生电感和阻抗。

- 其他规则 :

- 器件引脚的走线尽可能宽,减小走线阻抗和寄生电感;

- 避免在功率回路上打过孔,过孔会增加寄生电感;

- 栅极走线采用 50Ω 阻抗匹配,避免信号反射导致的振铃。

9.3 热设计优化方案

- 封装散热优化:优先选择底部带散热焊盘的 DFN、QFN、LGA 封装,散热焊盘直接连接内层地平面,增加散热过孔,过孔数量尽可能多,孔径 0.3mm~0.5mm,降低热阻。

- 散热器设计:TO 封装器件必须匹配合适的散热器,填充导热硅脂,降低 Rth (ca);消费类无散热器设计,必须通过 PCB 铜箔散热,器件周围铺大面积铜箔,增加散热面积。

- 损耗优化:通过软开关拓扑、优化死区时间、优化开关频率,降低器件总损耗,从根源上减小发热量。

9.4 EMI 设计与振铃抑制方法

- 振铃抑制 :

- 优化栅极电阻,适当增大 Rg,减缓开关速度,抑制电压振铃;

- 增加 RC 缓冲电路,并联在器件的漏极和源极之间,吸收尖峰电压;

- 优化 PCB 布局,减小功率回路寄生电感,从根源上抑制振铃。

- EMI 优化 :

- 采用扩频技术,降低开关频率的峰值噪声;

- 优化栅极驱动电阻,平衡开关速度和 EMI;

- 增加共模电感、X 电容、Y 电容,优化 EMI 滤波电路;

- 功率回路和信号回路进行屏蔽,避免辐射干扰。

第十章 总结与发展趋势

GaN HEMT 作为第三代宽禁带半导体的核心器件,凭借其高频、高效、高功率密度的核心优势,正在快速替代传统 Si MOSFET,成为功率电源领域的主流器件。未来,GaN 技术的发展将呈现三大趋势:

- 更高集成度:从分立器件向 GaN IC 发展,实现控制器、驱动、GaN 功率管、保护电路的全集成,大幅简化设计,降低应用门槛;

- 更高性能与更低成本:工艺持续优化,导通电阻和开关损耗进一步降低,Si 衬底 GaN 技术成熟度持续提升,成本不断下降,向更多中低端应用渗透;

- 更广泛的应用场景:从消费类快充,向车载新能源、光伏储能、工业变频器、数据中心、航空航天等领域全面拓展,成为电力电子行业的核心基石。

本文覆盖了 GaN HEMT从基础认知到工程应用的核心知识,所有内容均贴合工业级设计实操,可用于器件选型、电路设计、问题排查。欢迎在评论区交流工程设计中的问题与经验。如果本文对你有帮助,欢迎点赞、收藏、关注,后续会持续分享更多电路硬件设计的实战内容。