在数字电路设计中,三态门扮演着至关重要的角色。它是Verilog硬件描述语言中的一个基本元素,用于实现复杂电路的设计与模拟。

今天,我们一起来探讨三态门的基本原理、在Verilog中的实现方式。

一、什么是三态门?

三态门,简单来说,是一种具有三种输出状态的逻辑门电路,即逻辑"0"、逻辑"1"和高阻态(High Impedance,通常用字母"Z"表示)。

在正常的逻辑电路中,输出只有"0"和"1"两种状态,但三态门增加了高阻态这一特殊状态,使得电路在某些情况下可以呈现出高阻抗的特性,就好像电路被断开一样。

这种特性使得三态门在总线通信、数据选择等场景中有着广泛的应用。

二、三态门的工作原理

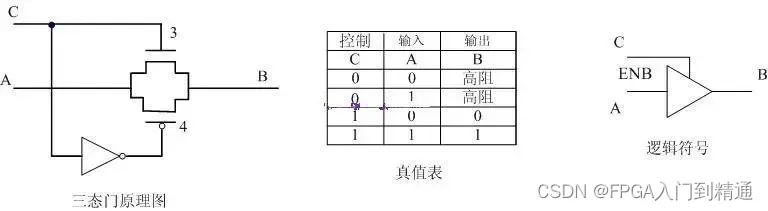

三态门通常有一个使能(Enable)信号,用于控制门的输出状态,如下图所示,其中C端口就是使能信号。

当使能信号C有效时,三态门直通,B端口等于A端口;

当使能信号C无效时,三态门的输出则呈现为高阻态。

三、Verilog 中三态门的实现

1、实现方式1

module tri_state_gate(

output out,

input in,

input en

);

assign out = en? in : 'bz;

endmodule

说明:

模块有三个端口: out 是输出端口, in 是输入端口, en 是使能端口。

assign 语句用于根据使能信号 en 的值来决定输出 out 的值。

当 en 为高电平时,out 等于输入 in;

当 en 为低电平时, out 为高阻态 'bz' 。

2、inout信号端口

在verilog中以使用 inout 类型的端口来实现双向的三态门,这在总线通信等场景中非常有用。

module bi_directional_gate(

inout wire data_io

);

wire data_in;

wire data_out;

wire en;

// 将双向信号拆分成输入、输出和使能信号

assign data_io = en? data_out : 1'bz;

assign data_in = data_io;

endmodule

说明:

data_io 是一个双向的 inout 类型端口。

当 en为高电平时,data_io 作为输出端口,输出 data_out的值;

当en为低电平时,data_io 作为输入端口, data_in 接收外部输入的值。

如果需要更多学习资料和源码,想要学习FPGA实战入门进阶,请阅读下面这篇文章: