触发FPGA 进行配置的方式有两种,一种是断电后上电,另一种是在FPGA运行过程中,将PROGRAM 管脚拉低。将PROGRAM 管脚拉低500ns 以上就可以触发FPGA 进行重构。

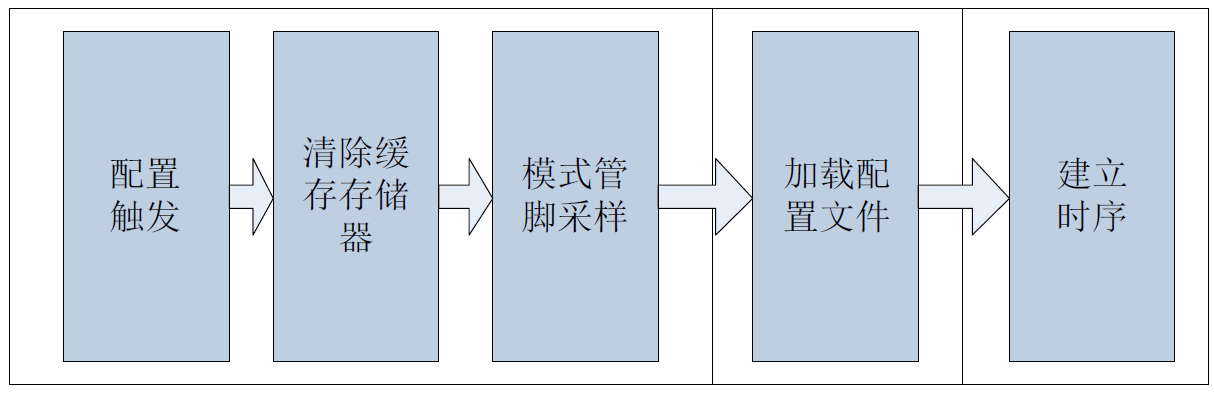

FPGA 的配置过程大致可以分为:配置的触发和建立阶段、加载配置文件和建立时序。

其详细步骤可以分为5 个。

(1)配置触发

在运行过程中,将FPGA 的PROGRAM 管脚置低500ns 以上会触发重置。上电重置是复位整个FPGA,不仅仅是进入重置过程,而且对其他器件会有影响。

(2)清除配置存储器

将PROGRAM 管脚拉低500ns 以上会触发FPGA 重置。触发后,DONE 和INIT 两个管脚会被拉低,并开始清除配置存储器。INIT 管脚被拉高表示清理完成。

(3)配置管脚采样

将INIT 管脚拉高代表配置初始化完成,开始进入采样阶段。FPGA 会读取配置模式管脚M[2:0]上的数据,确定配置模式。

(4)加载配置文件

确定配置模式以后,FPGA 会从相应的数据管脚读取配置文件中的数据,根据配置命令和配置数据完成对FPGA 的配置。

(5)建立序列

建立序列是配置流程中的最后一个步骤。重构被触发后,DONE 管脚会一直被拉低。当配置文件加载完成,时序建立后,DONE 管脚被拉高,表示配置过程完成。