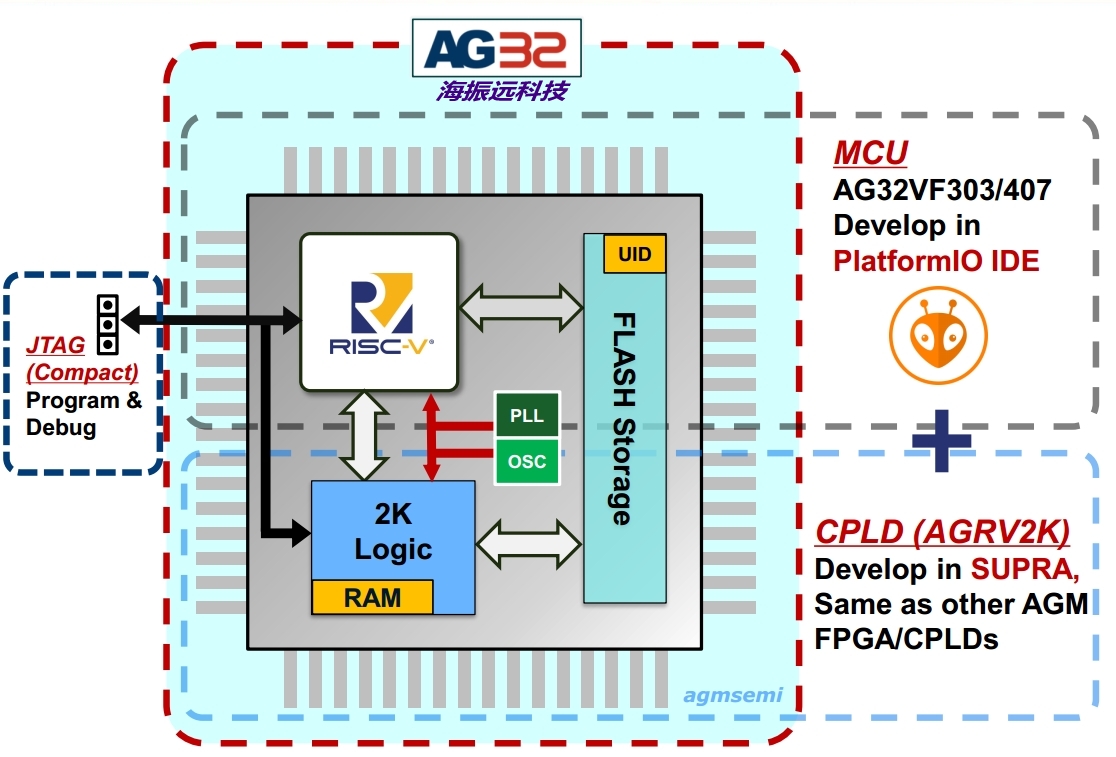

AG32是一款基于RISC-V内核的MCU,集成了可编程逻辑单元(CPLD),提供灵活的硬件设计能力。

本指南旨在为硬件设计人员提供AG32芯片的核心设计要点,涵盖电源、时钟、接口配置等关键方面,确保系统稳定性和性能优化。

1. HSE 外部晶体

范围:4~16MHz,推荐使用8MHz。

2. 电源设计

VDD/VDDA范围均为3.15~3.45V。CPLD对电源纹波要求较高,VDDA前需加磁珠,VDD33前也建议加磁珠。

3. 端口配置

ADC、DAC、CMP、USB、OSC、JTAG端口不可重新映射,其余数字端口可重映射至带IO的PIN。

4. 调试接口

支持SWD下载,使用SWDCLK(TCK)、SWDIO(TMS)、GND即可。MCU和CPLD共用此接口。建议将nRST引出至下载器的nRST,并在ini中设置:upload_srst = true。

5. 串口下载

仅支持UART0,不可重映射。需设置BOOT0(高)、BOOT1(低)。

6. BOOT0 配置

建议通过电阻接地,避免直接接地。调试时若烧录错误导致系统异常,可尝试将BOOT0拉高上电,以暂停用户程序并重新下载。

(未完待续)

本指南总结了AG32硬件设计的核心注意事项,涵盖电源、时钟、接口和调试等关键环节。设计时需结合具体应用场景,参考官方文档和海振远科技提供的参考设计,确保系统可靠性和性能优化。