| 上一篇 | 下一篇 |

|---|---|

| DMA(1) |

目 录

4)软件触发及对比

软件触发就是 Memory-to-Memory 模式

对于 Memory-to-Memory 模式(软件触发),DMA工作流程略有不同:

- CPU 配置通道(包括使能 Mem-to-Mem 模式)

- CPU 写 EN=1 → 立即触发一次完整块传输

- 无需外设请求

- 仲裁仅在多个 Mem-to-Mem 通道同时启动时起作用(较少见)

软件触发的表现形式就是代码中的一个命令,比如说当按键按下执行软件触发,使得一个数组从这块内存传输到另一块内存。

和硬件触发的对比总结表 :

| 特性 | 软件触发(Software Trigger) | 硬件触发(Hardware Trigger) |

|---|---|---|

| 触发源 | CPU 写 DMA 使能位 | 外设发出 DMA 请求信号(DREQ) |

| 是否需要外设 | ❌ 不需要(仅用于 Mem-to-Mem) | ✅ 必须有外设且使能 DMA 请求 |

| 传输粒度 | 一次性完成整个块(NDTR 次) | 每次外设请求传输 1 个数据单元 |

| 启动时机 | 配置后立即开始 | 等待外设事件发生 |

| 典型方向 | Memory ↔ Memory | Peripheral ↔ Memory |

| 是否可循环 | 可配置,但通常单次 | 常配合循环模式实现流式传输 |

| CPU 干预 | 启动时需 CPU,之后无需 | 启动后完全自动,零 CPU 干预 |

5)数据传输流向

在 STM32F1 中,传输的数据在物理上会短暂通过 DMA 控制器的内部数据通路,但不会被存储或缓冲(即单次传输)。其他 F4/F7 之类的内部有FIFO的,DMA可以暂存数据。

由于DMA 内部没有存储数据的缓冲区(F1 无 FIFO),所以它是一边读一边写,几乎是"直通"式的搬运。

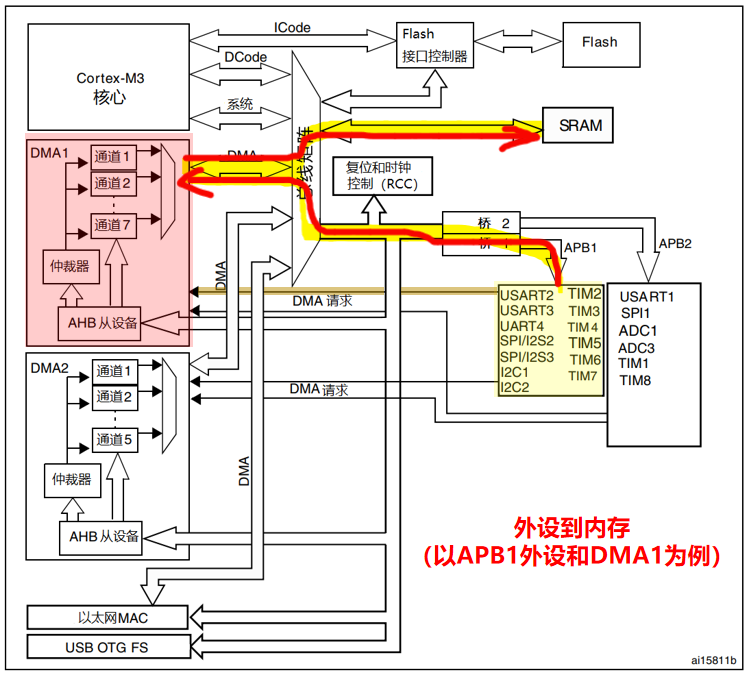

5.1)硬件触发

SRAM →(AHB 总线)→ DMA 控制器 →(APB 总线)→ 外设 DR 数据寄存器

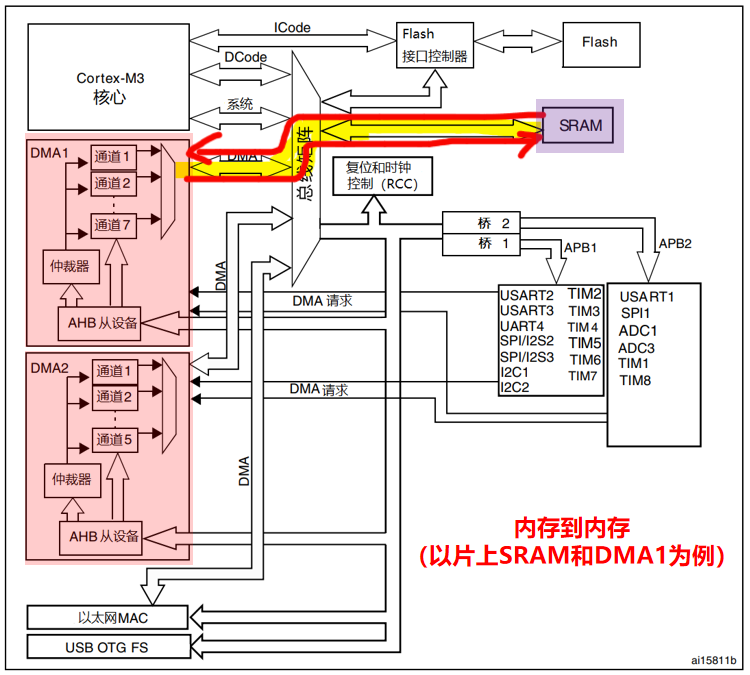

5.2)软件触发

SRAM →(AHB 总线)→ DMA 控制器 →(APB 总线)→ SRAM

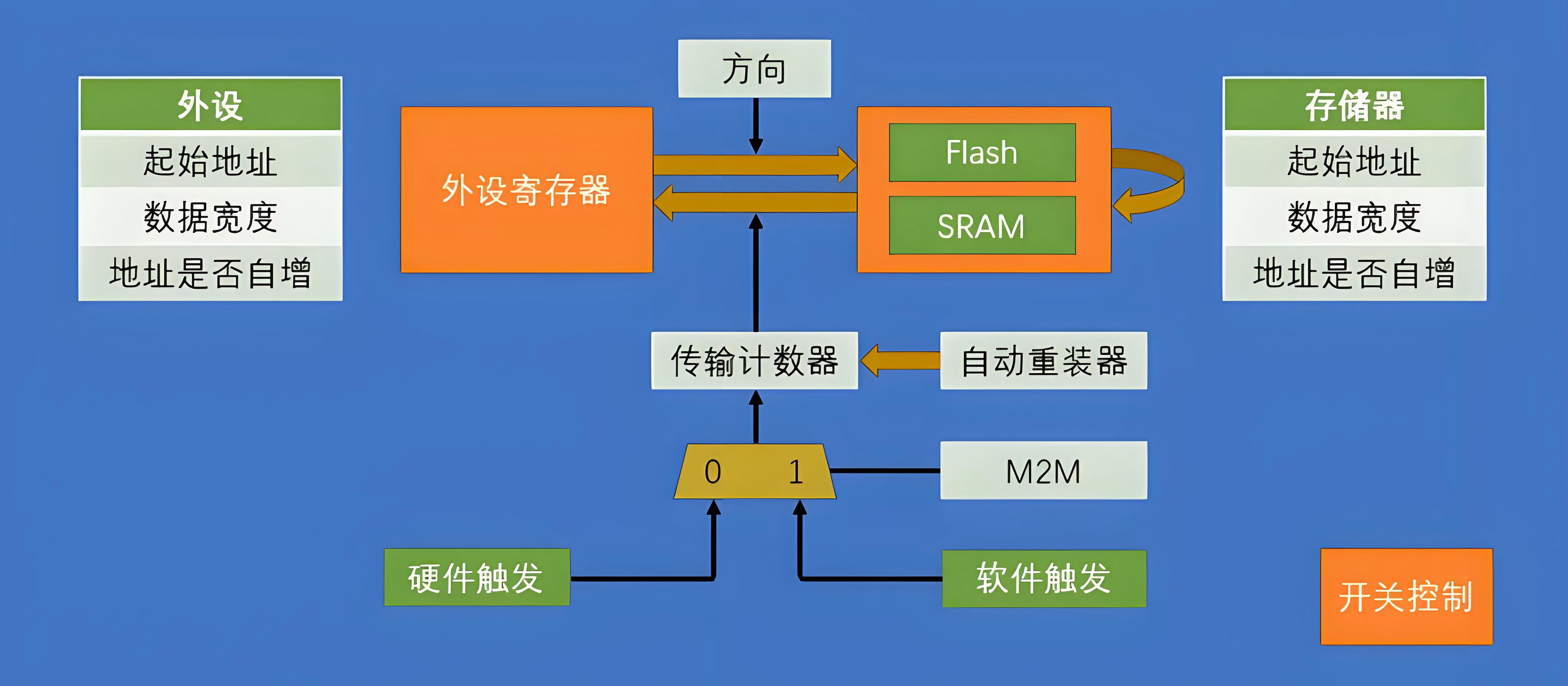

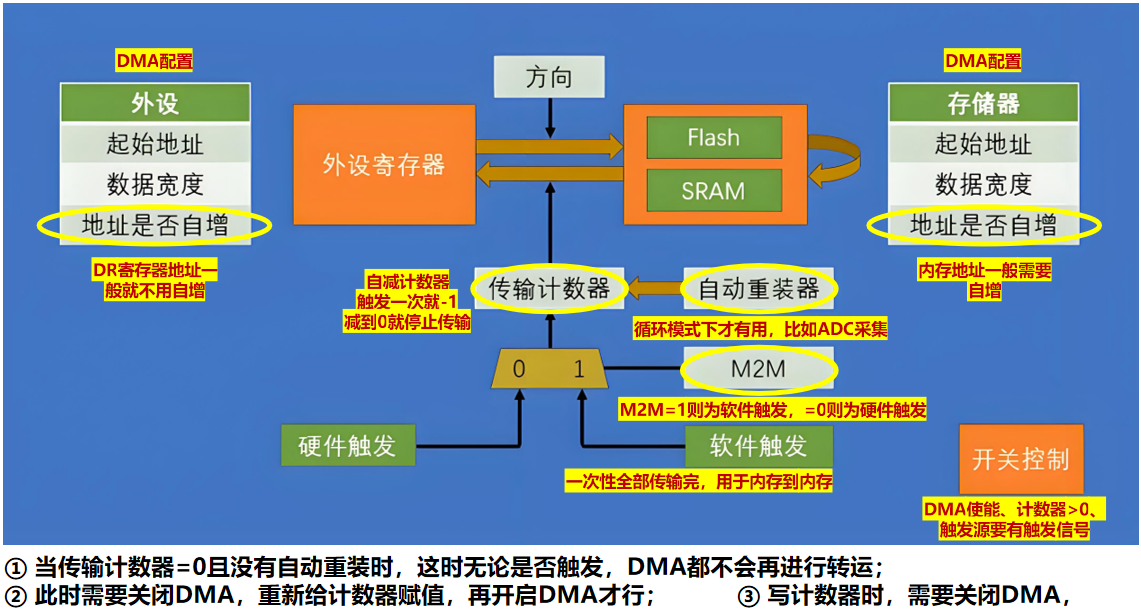

6)DMA 传输的宏观流程图

有一些细节没写出来,前面已经讲的足够细致了。

不要把数据宽度和计数器的值搞混了。

如果是内存到内存,那么只需要在途中左上角那里的外设DMA配置处配置内存DMA即可(地址填内存地址、设为增量模式、单次模式),他虽然叫外设DMA配置,但也只是ST官方这么叫而已,其实本质上就是两个配置项,其中一个是源,一个是目标。