关键字:FDCAN, BRS bit

1. 问题描述

客户在使用FDCAN协议,仲裁段波特率配置位1Mbit/s,数据段波特率配置为5Mbit/s

时,发现FDCAN发送功能异常。

2. 问题的测试和分析

首先建议客户使用IC内部回环模式进行测试,发现5M时没有问题,确认不大可能是软件

上的问题。之后同客户进行现场调试,观察FDCAN波形并分析问题产生的具体原因。

建议客户降低数据段波特率进行测试,发现降低数据段波特率后,可以正常通讯,下面是

波特率降下来后正常通讯的数据包的波形:

2.1. 对 FDCAN总线上数据包的波形进行分析

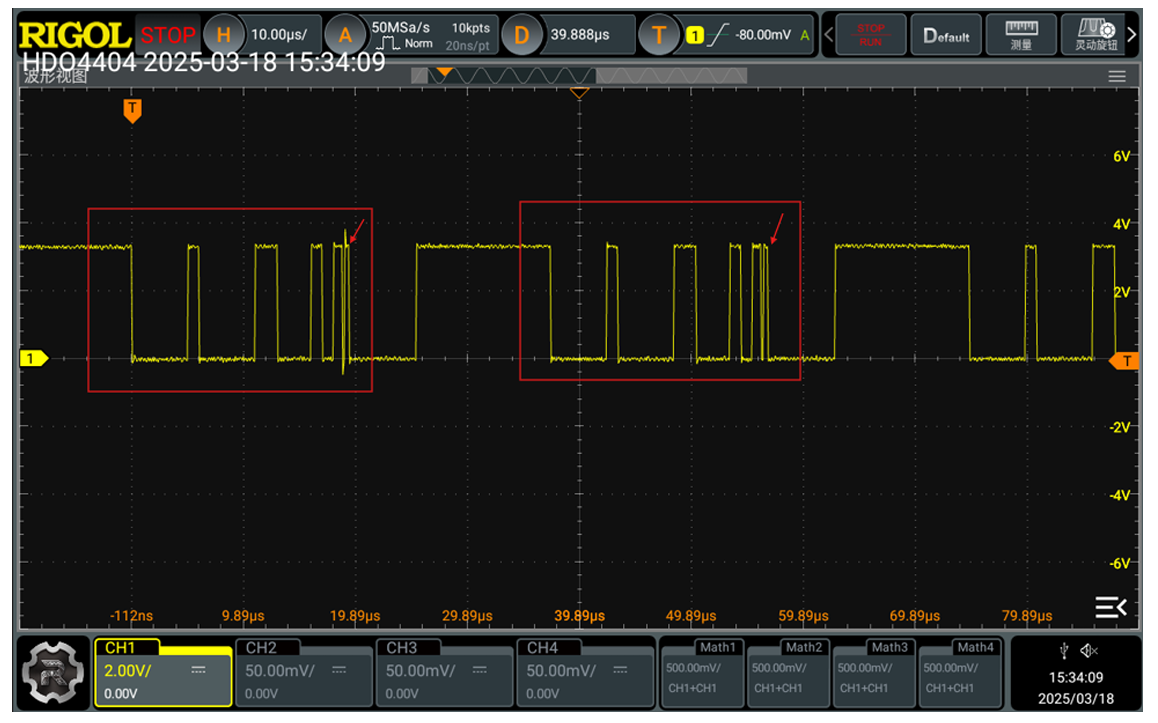

使用示波器抓取FDCAN 有问题的波形并进行分析,下面是有问题的波形,红色框中是

两个有问题的数据包,发生错误时数据包发送会被停止(红色箭头部分),由于使能了

FDCAN的数据包发送失败的自动重传功能,因此,数据包没成功发送时FDCAN硬件会再

次自动重传数据包。

图1. 有问题的波形

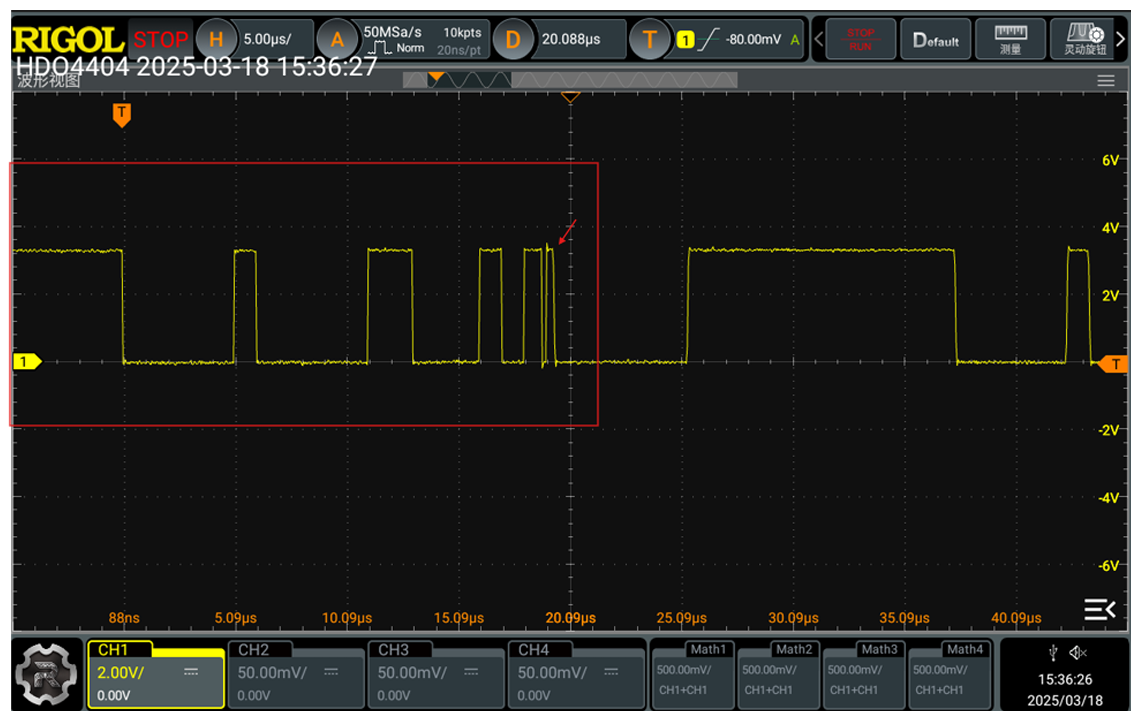

对上图的波形进行放大:

继续放大:

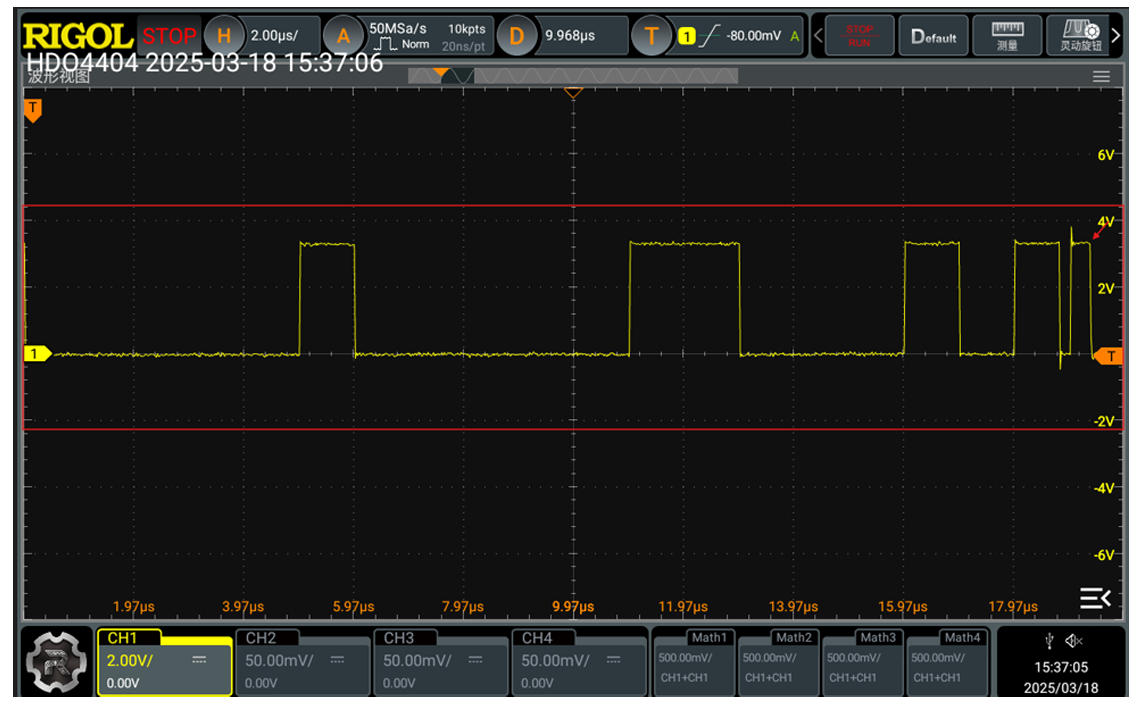

把上图红色箭头部分的波形继续放大,可以看到下面的波形,图中红色箭头指向的为

BRS 位,正是在BRS位时FDCAN数据包传输出了问题,发现数据出错后FDCAN外设将

停止发送数据并发出主动错误帧到总线上:

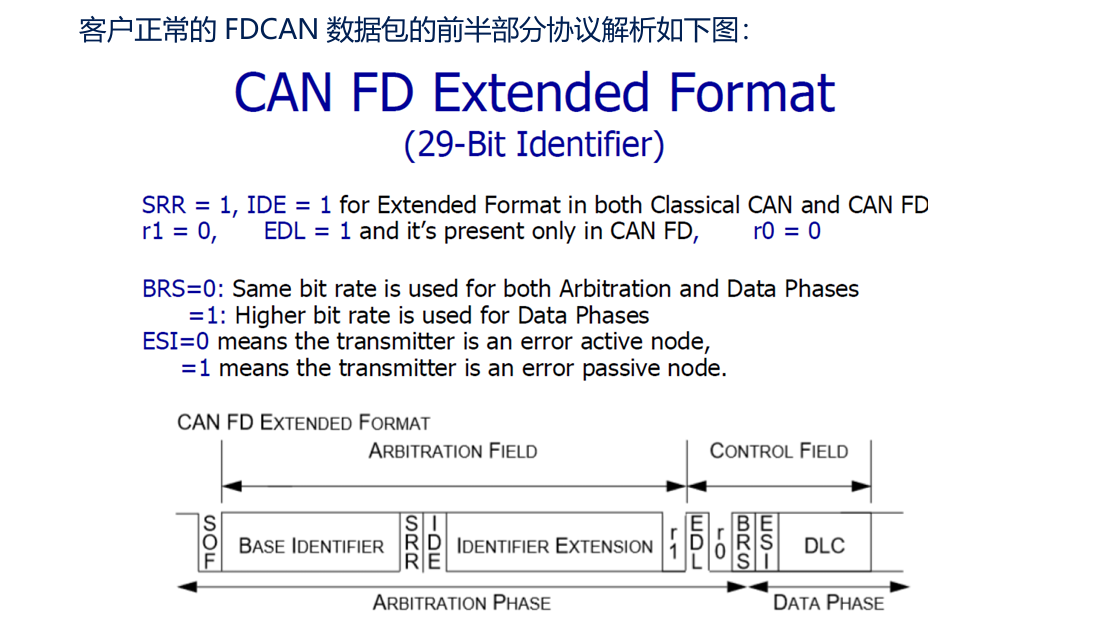

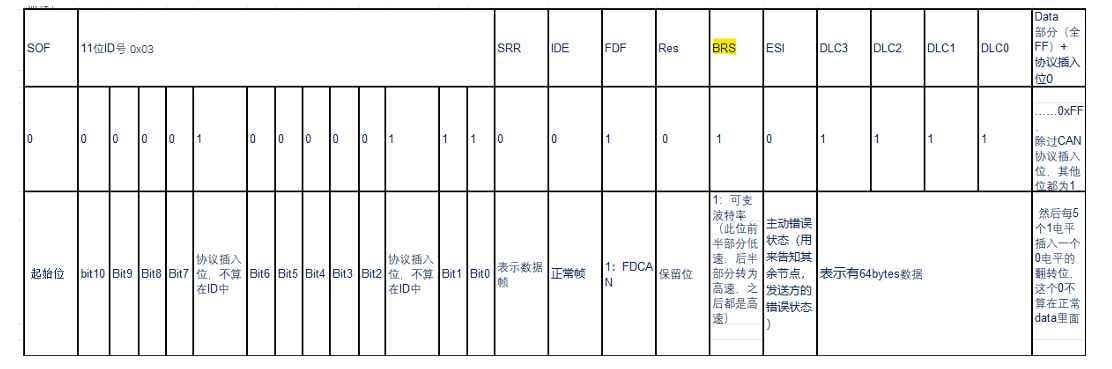

客户正常的FDCAN数据包的前半部分协议解析如下图:

客户产品在FDCAN发出BRS位的后半部分出现了问题,BRS之后的DLC位信息没有出

现在总线上,出现的是CAN协议中的错误帧。

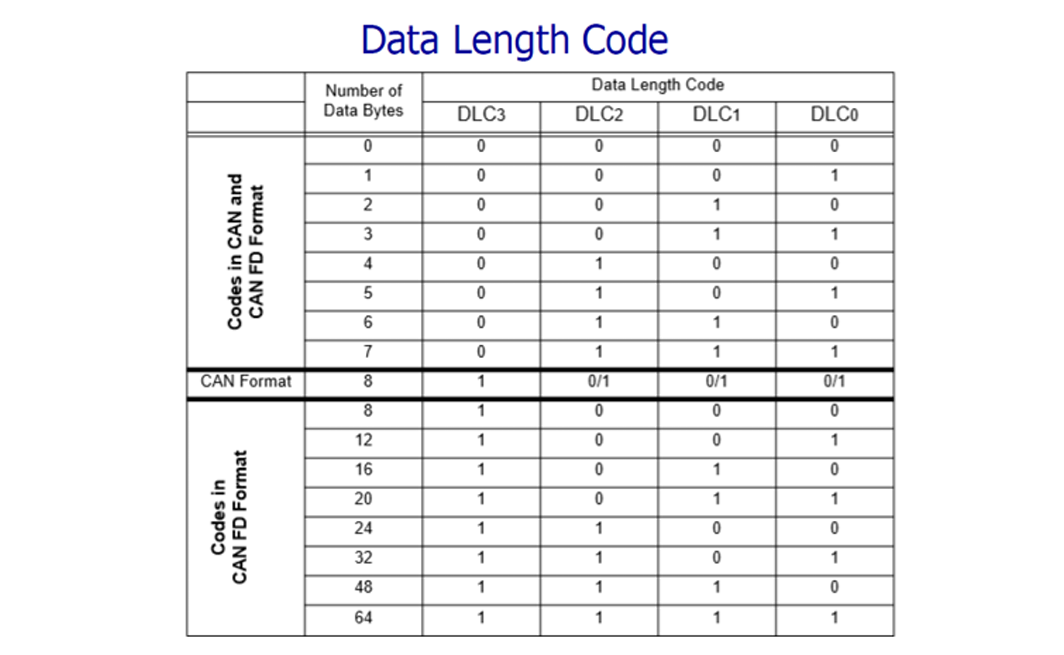

BRS (Bit Rate Switch) 为位速率转换开关,当BRS为隐形位(1)时,表示转换可变速

率,即发送节点在BRS位的采样点,将会切换到高速传输的时钟模式,后续其他接收节点也

必须使用转换位时钟模式。在CRC界定符的采样点,所有节点的波特率将会再切换回仲裁场

的波特率。也就是说,所有CAN FD节点都有两种类型的波特率。

例如:低波特率1MBit/s,采样点75%,高波特率2MBit/s,采样点80%;

当低速率向高速率切换,BRS位宽如下:

BRS 位宽=( 1us ×75%)+( 0.5us ×20%)= 850ns

BRS 位宽等于低波特率位的宽度中采样点之前的段加上高波特率位的宽度中采样点之后的

段。因此BRS位会存在波特率切换的过程。

客户产品问题就是出现在BRS位上,由于PCB layout问题,造成BRS高速段5Mbit/s

条件下波形异常,进而导致通讯异常。

3. 结论

当FDCAN数据段波特率增加时,也同时需要更好的PCB Layout来支撑。如果数据段波

特率增加时通讯不正常,降低波特率数据通讯就可以正常进行时,建议检查PCB Layout。

意法半导体公司及其子公司 ("ST")保留随时对 ST 产品和 / 或本文档进行变更的权利,恕不另行通知。买方在订货之前应获取关于 ST 产 品的最新信息。 ST 产品的销售依照订单确认时的相关 ST 销售条款。 买方自行负责对 ST 产品的选择和使用, ST 概不承担与应用协助或买方产品设计相关的任何责任。 ST 不对任何知识产权进行任何明示或默示的授权或许可。 转售的 ST 产品如有不同于此处提供的信息的规定,将导致 ST 针对该产品授予的任何保证失效。 ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息,请参考 www.st.com/trademarks。所有其他产品或服务名称均为其 各自所有者的财 产。 本文档是ST中国本地团队的技术性文章,旨在交流与分享,并期望借此给予客户产品应用上足够的帮助或提醒。若文中内容存有局限或与ST 官网资料不一致,请以实际应用验证结果和ST官网最新发布的内容为准。您拥有完全自主权是否采纳本文档(包括代码,电路图等)信息, 我们也不承担因使用或采纳本文档内容而导致的任何风险。 本文档中的信息取代本文档所有早期版本中提供的信息。 © 2020 STMicroelectronics - 保留所有权利