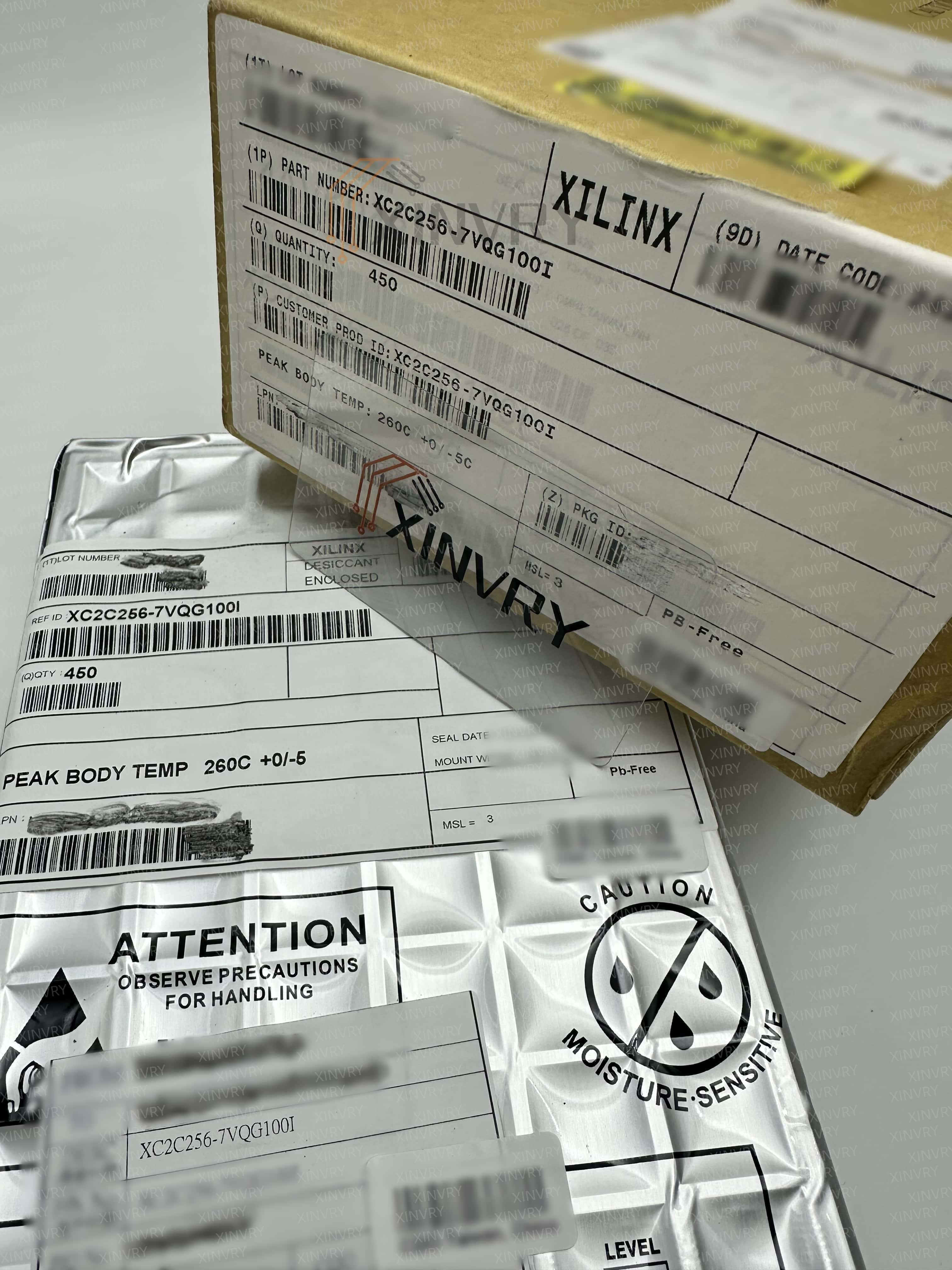

XC2C256-7VQG100I 赛灵思 Xilinx CoolRunner-II 系列的一款 256 宏单元(macrocell)级别的复杂可编程逻辑器件(CPLD)。该器件定位于超低功耗、瞬时就绪(instant-on)且适合 1.8 V 供电系统的小型化控制与接口场景,常以 100 引脚 VQFP 封装出现,集成度适中、I/O 密度高、且支持在系统(ISP)编程与 JTAG 调试。XC2C256 在设计上兼顾了传统 CPLD 的非挥发性配置与低功耗特点,同时提供比早期 CPLD 更先进的逻辑结构与更短的引脚到引脚延迟,因而在便携设备、工业控制、接口桥接与小规模逻辑替代中曾被广泛采用。

XC2C256-7VQG100I 的关键规格包括:256 个宏单元(macrocell);大约 6,000 系统门等效(system gates);约 80 个用户可用 I/O;器件内部划分为 16 个逻辑阵列块(LAB);典型的工作电压为 1.7--1.9 V(以 1.8 V 为优化目标);封装为 100 引脚 VQFP(VQG100);速度等级为 "-7"(器件在文档中对引脚到引脚传播延迟与最大工作频率给出 5.7 ns 至约 6.7 ns 的典型/上限值,对应最高可用的局部时序频率区间可达数百 MHz,实际能达到的系统频率受具体互连、负载与布局约束影响)。

CoolRunner-II 的逻辑资源以宏单元(macrocell)为基本构建块,每个宏单元提供可编程的组合逻辑与触发器选项。若干宏单元组合成逻辑阵列块(Function Block / LAB),每个 LAB 内设有固定数量的输入入口点与产品项(product-term)资源,从而形成可扩展且可预测的逻辑实现密度。与传统大规模 FPGA 不同,CPLD 的内部互连和逻辑分布更加静态、确定性更强,因此在实现定制状态机、并行控制逻辑或 I/O 密集型 glue-logic 时更易于时序闭合与重现。CoolRunner-II 还在逻辑结构与 I/O 路径上进行了低功耗与低延迟优化,使得在 1.8 V 系统中能够实现极低的静态电流(datasheet 报告静态电流低至数十微安乃至更低)与较短的引脚-引脚延迟。

XC2C256 提供灵活的 I/O 管脚分组与输出驱动能力,支持多种常见电平标准并提供对 I/O-to-I/O 定时(I/O-to-I/O timing)的保证,这是许多 CPLD 在接口桥接场景中优于 FPGA 的一项重要特性。该家族支持 Schmitt Trigger 输入、典型的开漏/推挽输出模式、可编程驱动强度等功能,便于直接驱动多种外围器件与总线。CoolRunner-II 同时支持厂商提供的在系统编程(ISP)机制、JTAG 接口和"On-The-Fly"重编程能力(允许在不停止器件当前运行的情况下编程新的非挥发模式并在合适时机切换到新配置),从而在产品维护与现场升级上提供了灵活性。

赛灵思 Xilinx CoolRunner-II 系列CPLD

XC2C64A-7VQG44I XC2C32-6VQ44C XC2C384-7TQG144C

XC2C64A-7VQG44C XC2C32-6CP56I XC2C384-7FTG256C

XC2C64A-7VQG100I XC2C256-7VQG100I XC2C384-7FT256C

XC2C64A-7VQG100C XC2C2567VQG100I XC2C384-10TQG144I

XC2C64A-7VQ44I XC2C256-7VQG100C XC2C384-10TQG144C

XC2C64A-7VQ44C XC2C2567VQG100C XC2C384-10TQ144I

XC2C64A-7VQ100I XC2C256-7VQ100I XC2C384-10TQ144C

XC2C64A-7VQ100C XC2C256-7VQ100C XC2C384-10TQ144

XC2C64A-7QFG48I XC2C256-7TQG144I XC2C384-10PQG208C

XC2C64A-7QFG48C XC2C256-7TQG144C XC2C384-10FTG256I

XC2C64A-7CPG56I XC2C256-7TQ144I XC2C384-10FTG256C

XC2C64A7CPG56I XC2C256-7TQ144C XC2C384-10FT256I

XC2C64A-7CPG56C XC2C2567TQ144C XC2C384-10FT256C

XC2C64A-7CP56I XC2C256-7PQG208I XC2C384-10FGG324I

XC2C64A-7CP56C XC2C256-7FTG256I XC2C128-7CPG132I

XC2C64A-5VQG44C XC2C256-7FTG256C XC2C32A-6VQG44I

XC2C64A-5VQG100C XC2C256-7FT256I XC2C32A-6VQG44C

XC2C64A-5VQ44C XC2C256-7FT256C XC2C32A-6VQ44I

XC2C64A-5VQ100C XC2C256-7CPG132I XC2C32A-6VQ44C

XC2C64A-5QFG48C XC2C256-7CPG132C XC2C32A-6QFG32I

XC2C64A-5CPG56C XC2C256-7CP132I XC2C32A-6QFG32C

XC2C64A-5CP56C XC2C256-7CP132C XC2C32A-6CPG56I

XC2C512-10FG324I XC2C256-6VQG100C XC2C32A-6CPG56C

XC2C64-7VQ44C XC2C256-6VQ100C XC2C32A-6CP56I

XC2C64-7VQ100C XC2C256-6TQG144C XC2C32A-6CP56C

XC2C64-7CP56C XC2C256-6TQ144C XC2C32A-4VQG44C

XC2C512-7FTG256I XC2C256-6PQG208C XC2C32A-4VQ44C

XC2C512-7FTG256C XC2C256-6FTG256C XC2C32A-4QFG32C

XC2C512-7FT256I XC2C256-6FT256C XC2C32A-4CPG56C

XC2C512-7FT256C XC2C256-6CPG132C XC2C32A-4CP56C

XC2C512-10PQG208I XC2C512-10FGG324C XC2C128-7CPG132C

XC2C512-10PQG208C XC2C128-7VQG100I XC2C128-7CPG132

XC2C512-10PQ208I XC2C128-7VQG100C XC2C128-7CP132I

XC2C512-10PQ208C XC2C1287VQG100C XC2C128-7CP132C

XC2C512-10FTG256I XC2C128-7VQG100 XC2C128-6VQG100C

XC2C51210FTG256I XC2C128-7VQ100I XC2C128-6VQ100C

XC2C512-10FTG256C XC2C128-7VQ100C XC2C128-6TQ144C

XC2C512-10FT256I XC2C128-7TQG144I XC2C128-6CPG132C

XC2C512-10FT256C XC2C128-7TQG144C XC2C128-7TQ144C

XC2C512-10FGG324I XC2C128-7TQ144I