1. 本文背景与目标

- 为什么要在 U-Boot 阶段 点亮 MIPI 屏

- 提前验证硬件连线

- 启动画面(logo / splash)

- 辅助 Kernel 调试

- 本文适用范围

- 硬件:正点原子STM32MP257开发板

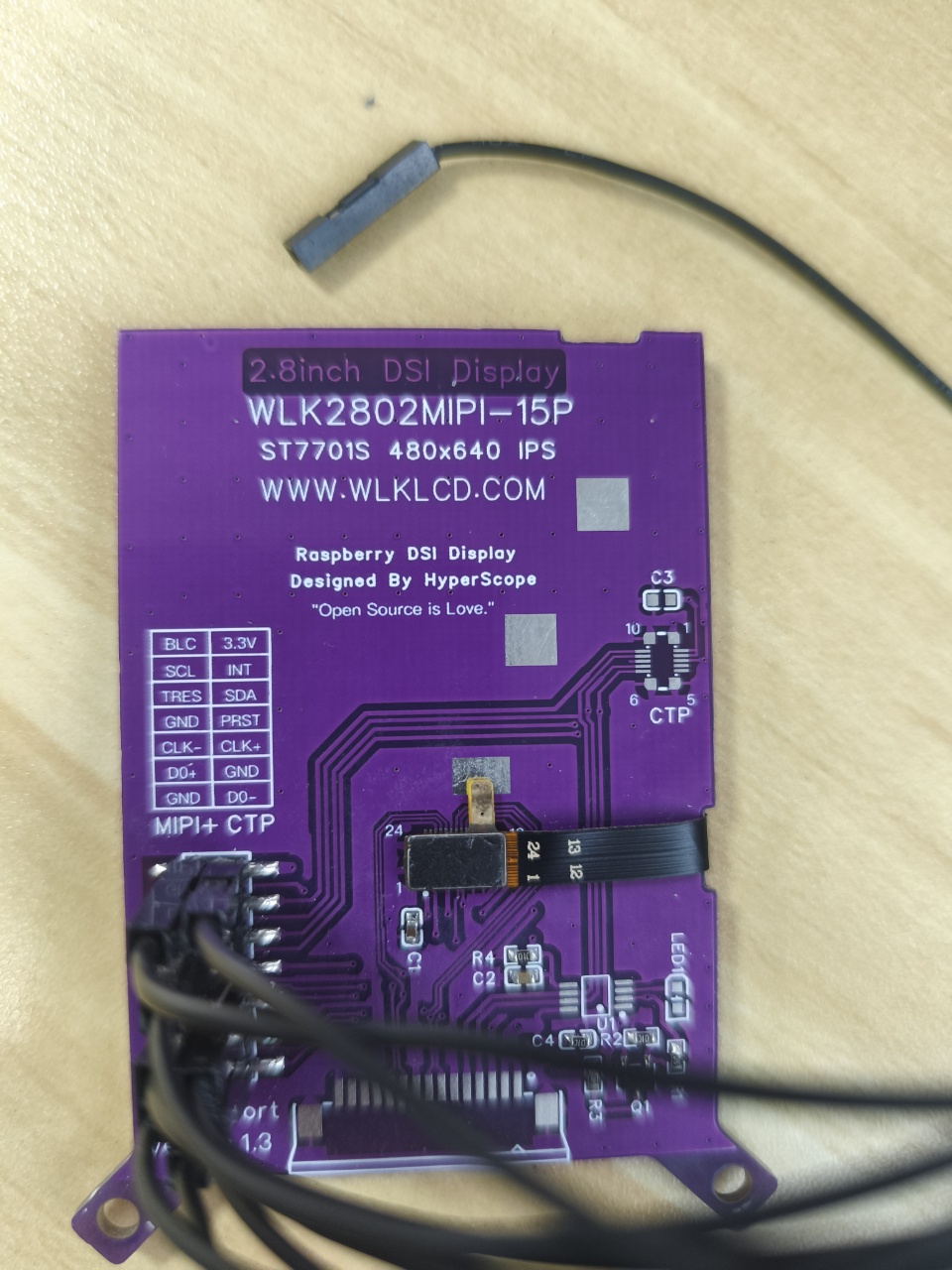

- 屏幕:正点原子5.5村MIPI屏幕(4 lane)/WLK2802MIPI-15P(1 lane)

- 软件:OpenSTLinux 6.6 + U-Boot

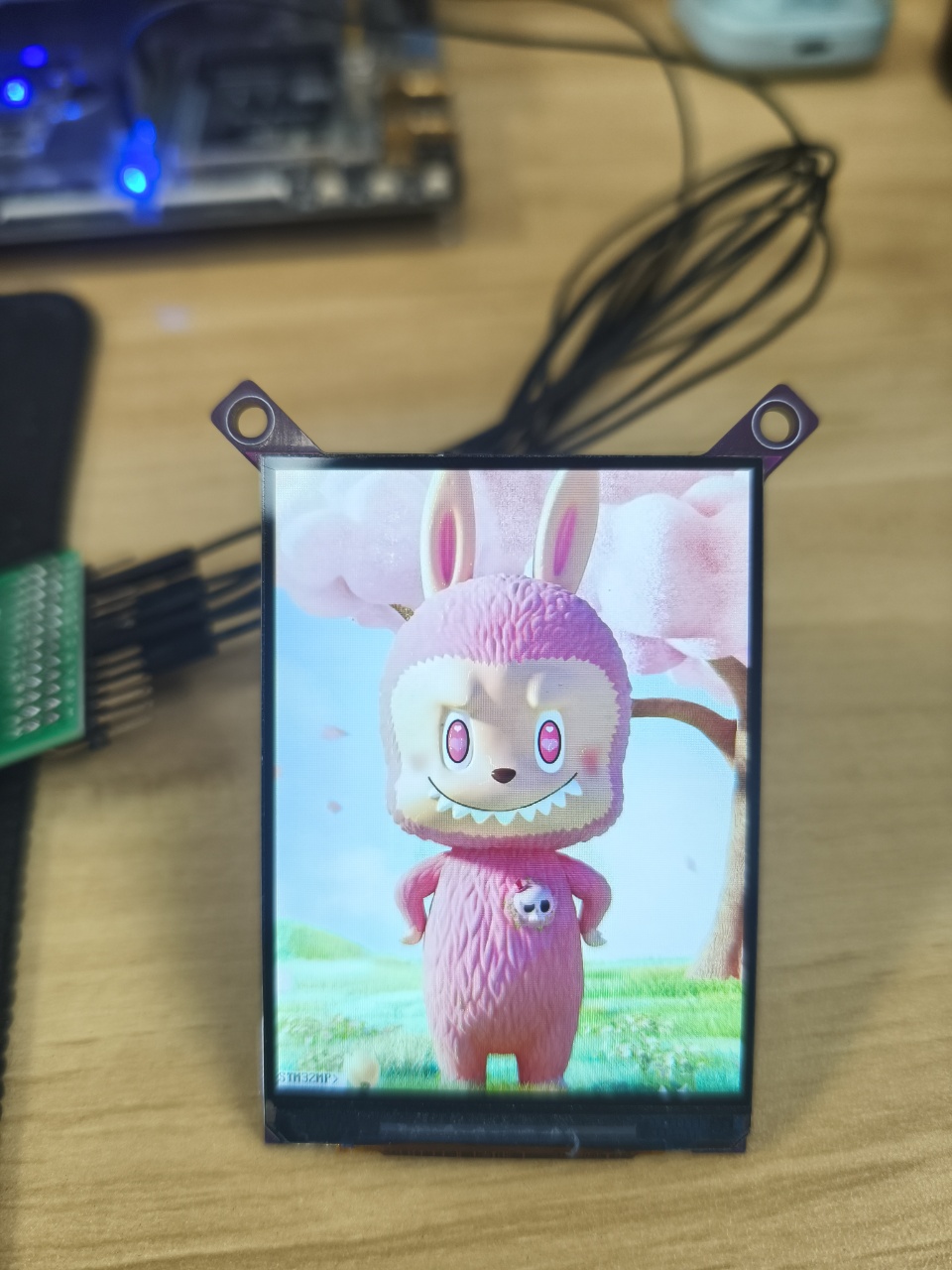

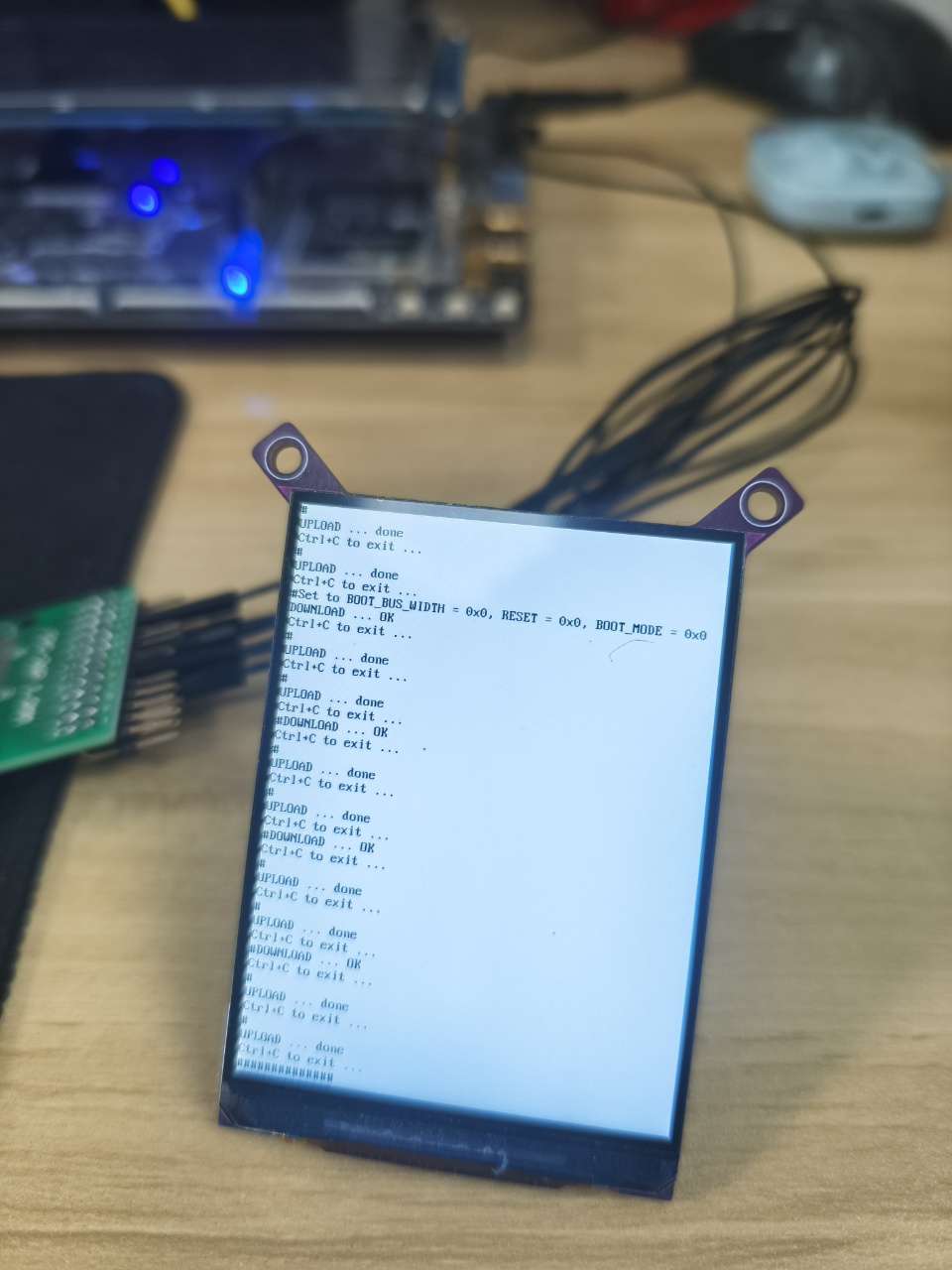

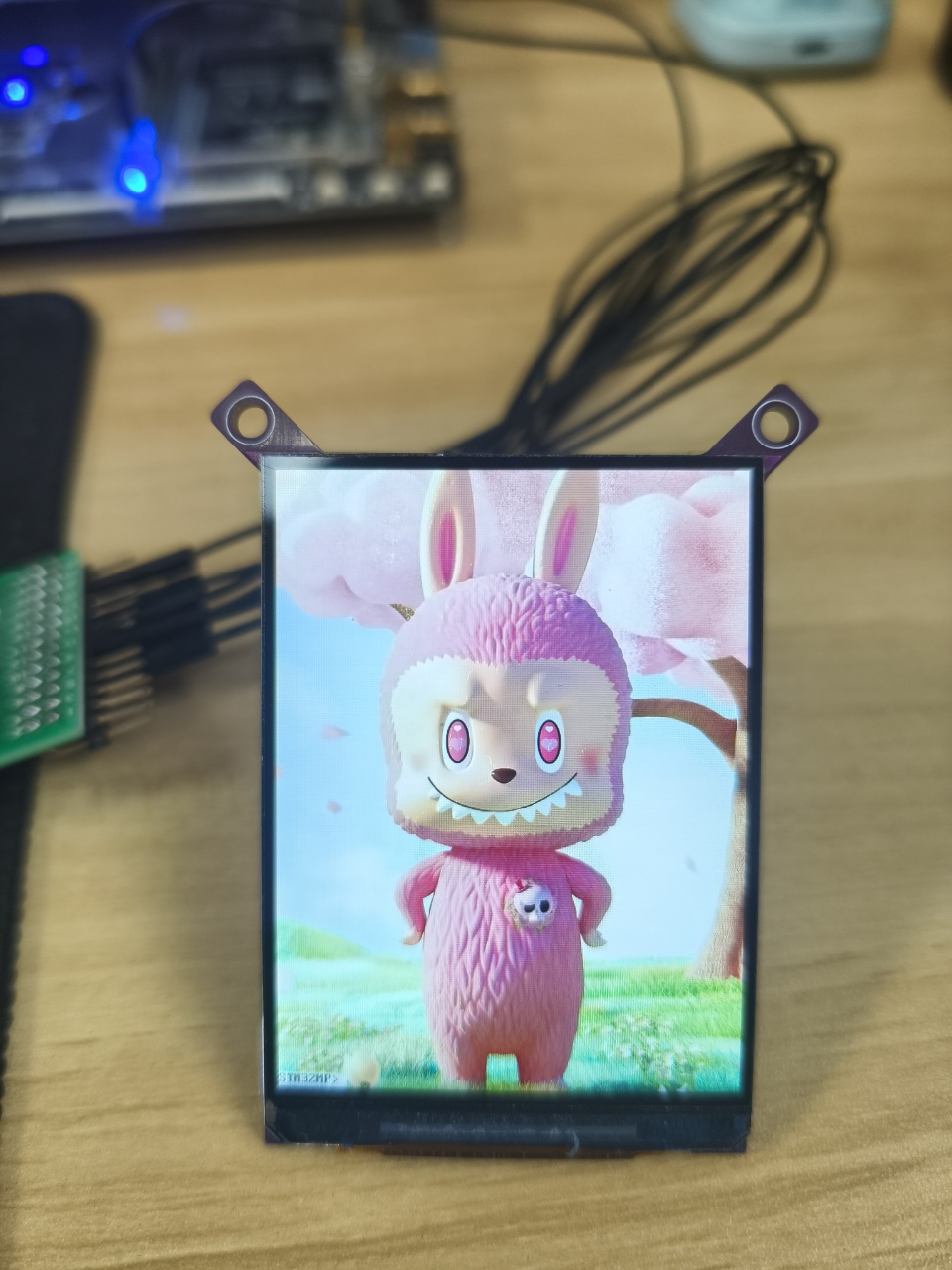

- 效果展示

2. STM32MP2 显示系统总体架构

2.1 显示链路总览

LTDC → DSI Host → MIPI D-PHY → LCD Panel- LTDC 的作用

- DSI Host 的作用

- D-PHY 与 Lane 的关系

2.2 参考手册 RM0457 中的显示模块

- RM0457 中涉及的模块章节

- LTDC

- DSI HOST

- DSI PHY(D-PHY)

3. RM0457 解析:DSI Host & Lane 能力

-

RM0457 中关于 DSI Lane 的说明

-

支持模式 - 本次只使用1/4 data lane + 1 clock lane

-

1 data lane + 1 clock lane

-

2 data lane + 1 clock lane

-

4 data lane + 1 clock lane

-

4. 设备树与驱动

正点原子5.5寸MIPI屏幕(4 lane)/WLK2802MIPI-15P(1 lane)设备树

/ {

...

panel_backlight: panel-backlight {

compatible = "gpio-backlight";

gpios = <&gpiob 0 GPIO_ACTIVE_HIGH>;

default-on;

status = "okay";

};

...

}; /*root*/

// DSI节点描述

&dsi {

status = "okay";

/* USER CODE BEGIN dsi */

vdd-supply = <&scmi_vddcore>;

vdda18-supply = <&scmi_v1v8>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dsi_in: endpoint {

remote-endpoint = <<dc_ep0_out>;

};

};

port@1 {

reg = <1>;

dsi_out: endpoint {

remote-endpoint = <&dsi_panel_in>;

};

};

};

panel_dsi: panel@0 {

compatible = "alientek,mipi-lcd";

//compatible = "wlk,w280bf036i";

reg = <0>;

//dsi-lanes = <4>;

reset-gpios = <&gpioi 11 GPIO_ACTIVE_LOW>;

backlight = <&panel_backlight>;

power-supply = <&vdd_5v>;

port {

dsi_panel_in: endpoint {

remote-endpoint = <&dsi_out>;

};

};

};

/* USER CODE END dsi */

};

// LTDC节点描述

<dc {

status = "okay";

/* USER CODE BEGIN ltdc */

default-on;

//rotation-memory = <<dc_sec_rotation>;

port {

#address-cells = <1>;

#size-cells = <0>;

ltdc_ep0_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&dsi_in>;

};

};

/* USER CODE END ltdc */

};驱动文件

-

drivers/video/Makefile

obj-y += panel-alientek-mipi.o obj-y += panel-w280bf036i-dsi.o -

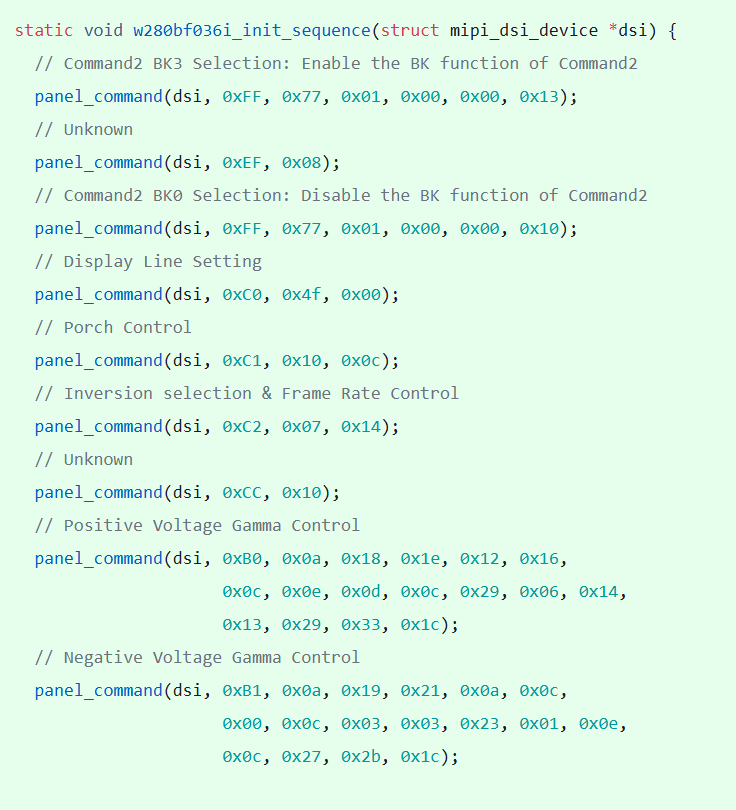

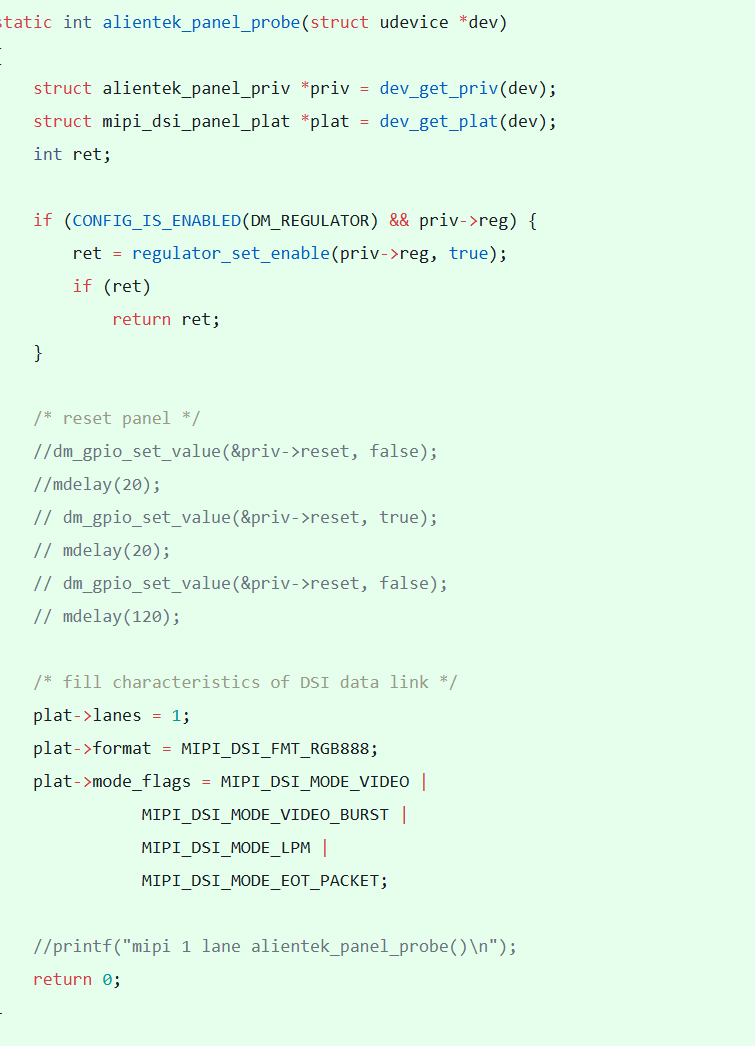

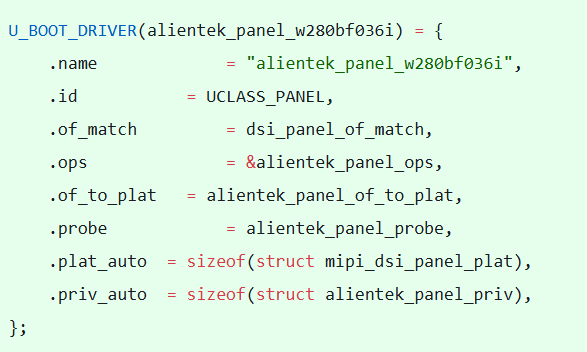

panel-alientek-mipi.c/panel-w280bf036i-dsi.c

-

正点原子5.5寸MIPI屏幕(4 lane)

-

WLK2802MIPI-15P(1 lane)

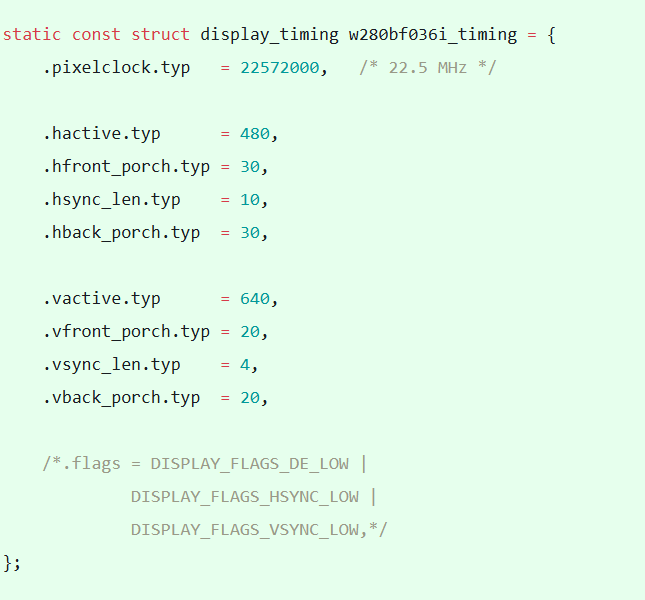

屏幕时序,一般由厂家提供

屏幕初始化参数,一般由厂家提供

初始化D-PHY参数(n lane/DSI图像格式/模式设置)

-

5. MIPI信号连接

MIPI告诉信号,要先把硬件引脚连接好

正点原子5.5寸MIPI屏幕(4 lane)直接将排线插入即可

WLK2802MIPI-15P(1 lane)硬件连接

DSI TP RST -----------------> TRES

DSI BL -----------------> BLC

DSI CK P -----------------> CLK+

DSI CK N -----------------> CLK-

DSI D0 P -----------------> D0+

DSI D0 N -----------------> D0-

板子3.3V -----------------> 3.3V

GND -----------------> GND

SCL/SDA/INT/PRST不用接

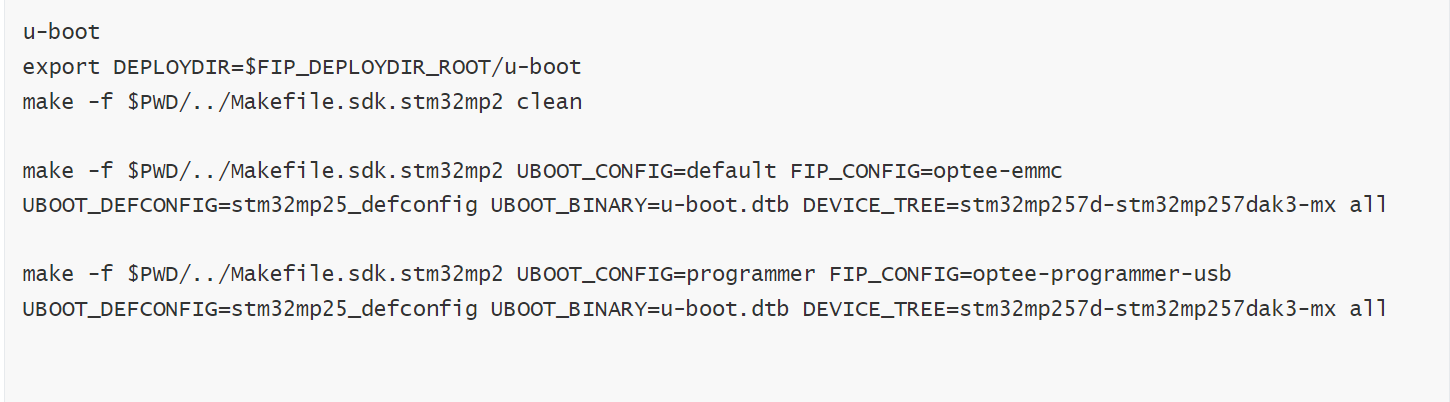

6. 编译测试

7. 板端验证